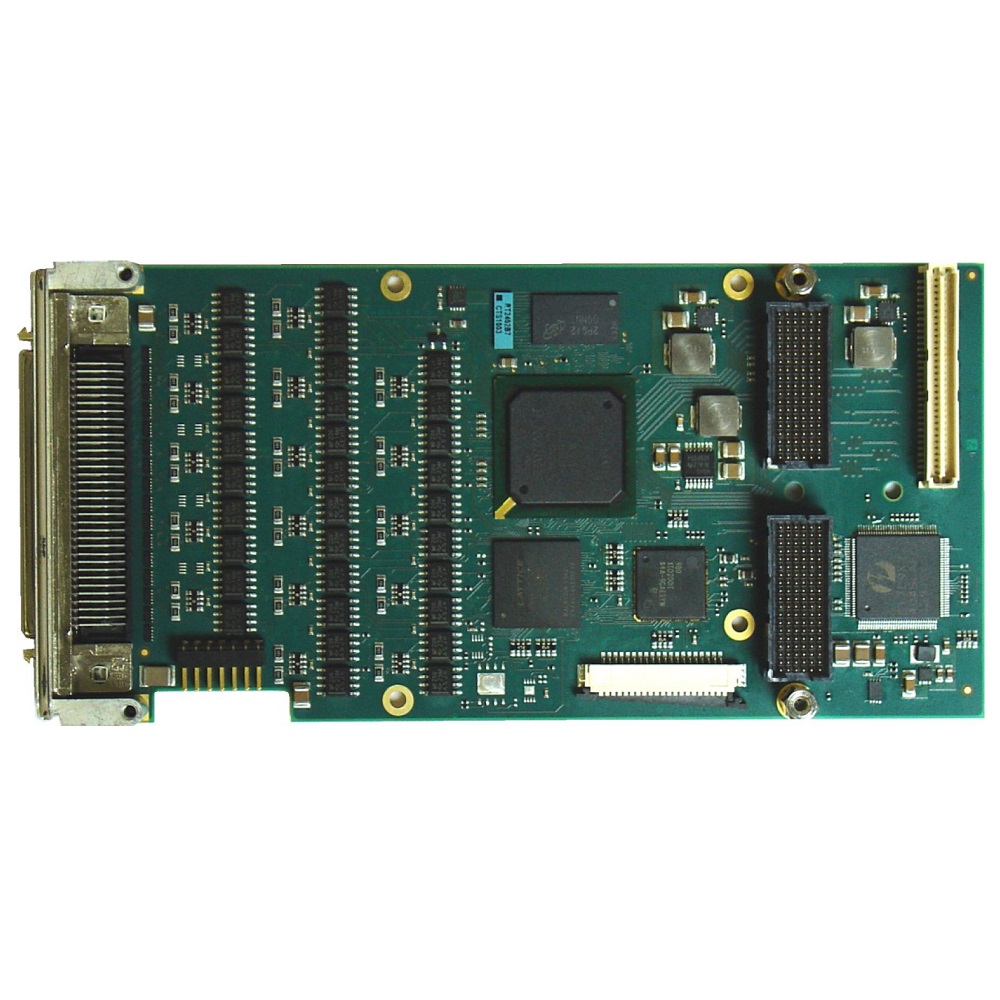

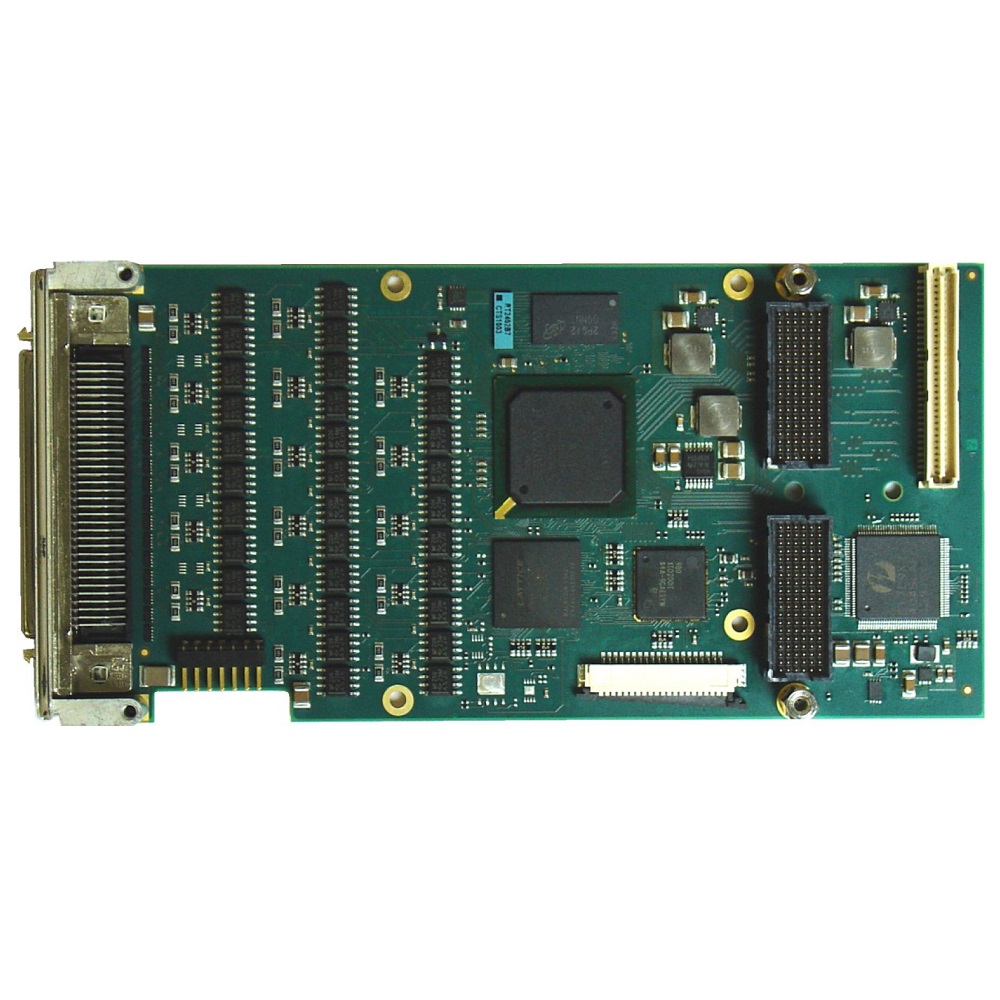

TXMC633 FPGA XMC-Modul mit 64 TTL- oder 32 Differenz-/M-LVDS-IOs

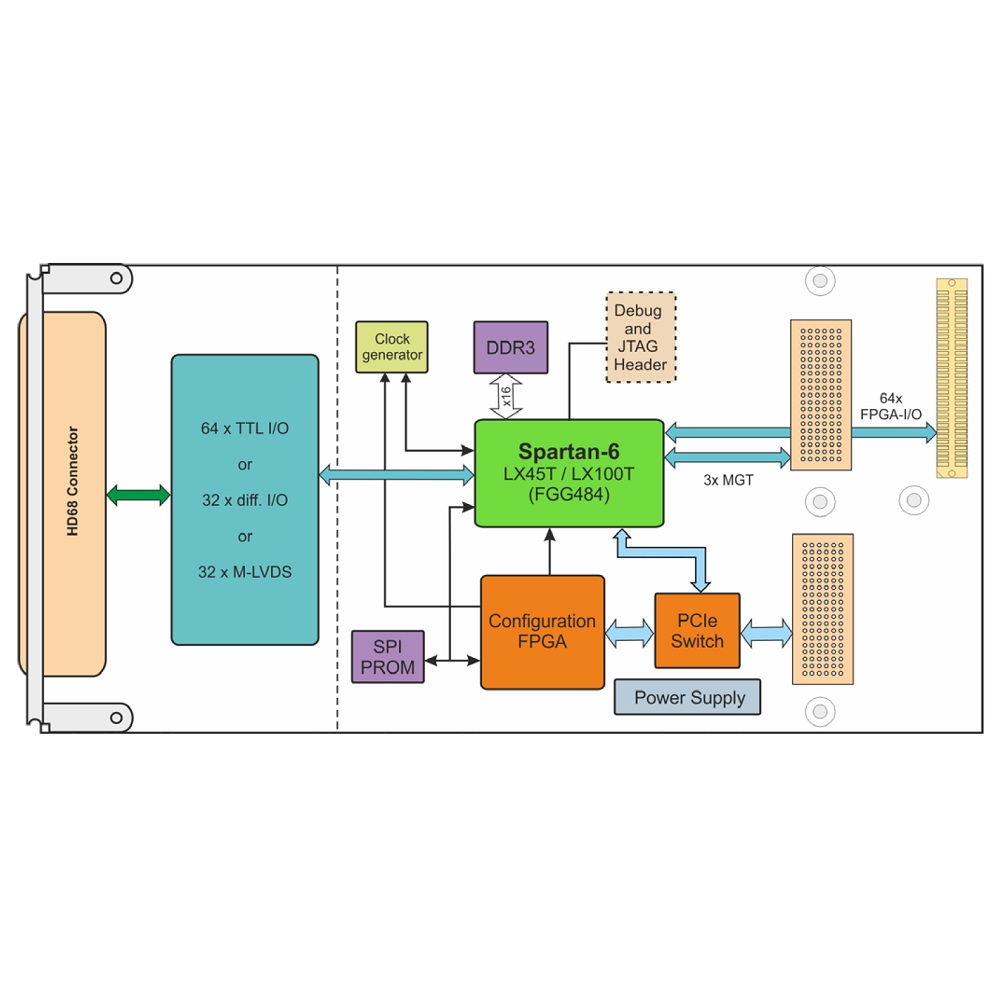

TXMC633 Blockschaltbild

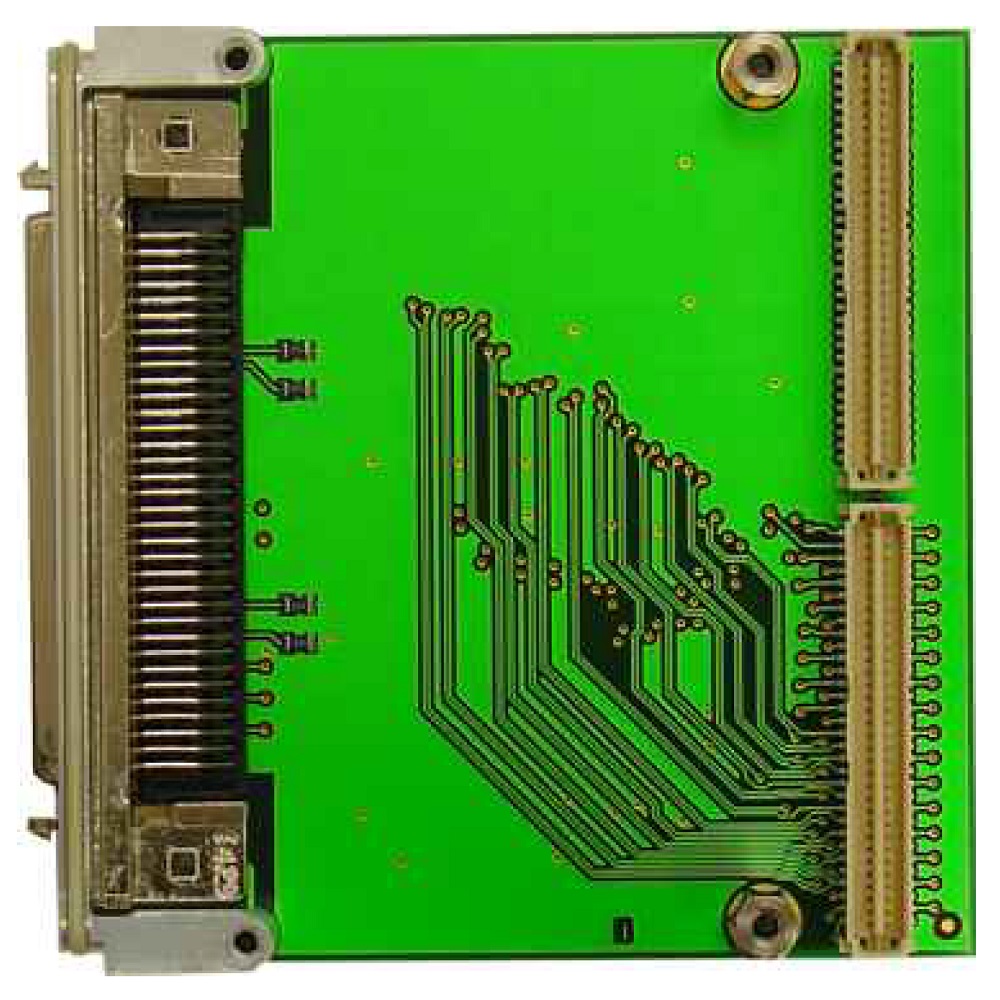

TPIM003-10 PIM-Modul mit 68-pin SCSI-3 Steckverbinder

TA104-10 1.8m Kabel mit HD-68 Steckern

TA203-10 68-pol. Klemmenblock mit HD-68 Buchse

TA304-10 Verbindungssatz aus 1.8m Kabel mit HD-68 Steckern und 68-pol. Klemmenblock

TA900-10 Program und Debug Box

TECHNISCHE BESCHREIBUNG

- XMC-Modul, 32-bit/33MHz PCI Interface, IEEE P1386.1 konform, PCI 2.2 konform, 3.3/5V Vio

- Spartan6 FPGA: TXMC633-1x mit Xilinx XC6SLX45T-2, TXMC633-2x mit Xilinx XC6SLX100T-2

- Serielles Flash

- 128 MB 16-bit DDR3 SDRAM

- 32 Mbit SPI-EEPROM für FPGA Konfiguration

- Flash im System und opt. über JTAG programmierbar

- I/O-Leitungen: 64 TTL-IOs (-x0R), 32 Differenz-IOs (-x1R), 32 TTL-IOs und 16 Differenz-IOs (-x2R), 32 M-LVDS I/O (-x3R) oder 32 TTL I/O und 16 M-LVDS I/O (-x4R) individuell als Ein-/Ausgang programmierbar

- Front- oder P14/16-IO

- -40°C .. +85°C Betriebstemperaturbereich

- Integrity, Windows, Linux, LynxOS, QNX und VxWorks Treiber lieferbar

- 5 Jahre Garantie

Bestellbezeichnungen

TXMC633-10R

XC6SLX45T-2 FPGA XMC-Modul mit 64 TTL-IOs

TXMC633-11R

XC6SLX45T-2 FPGA XMC-Modul mit 32 Differenz-IOs

TXMC633-12R

XC6SLX45T-2 FPGA XMC-Modul mit 32 TTL- und 16 Differenz-IOs

TXMC633-13R

XC6SLX45T-2 FPGA XMC-Modul mit 32 M-LVDS-IOs

TXMC633-14R

XC6SLX45T-2 FPGA XMC-Modul mit 32 TTL- und 16 M-LVDS-IOs

TXMC633-20R

XC6SLX100T-2 FPGA XMC-Modul mit 64 TTL-IOs

TXMC633-21R

XC6SLX100T-2 FPGA XMC-Modul mit 32 Differenz-IOs

TXMC633-22R

XC6SLX100T-2 FPGA XMC-Modul mit 32 TTL- und 16 Differenz-IOs

TXMC633-23R

XC6SLX100T-2 FPGA XMC-Modul mit 32 M-LVDS-IOs

TXMC633-24R

XC6SLX100T-2 FPGA XMC-Modul mit 32 TTL- und 16 M-LVDS-IOs

TA104-10R

1.8m Kabel mit HD-68 Steckern

TA203-10R

68-pin Klemmenblock mit HD-68 Buchse

TA304-10R

Verbindungssatz aus 1.8m Kabel mit HD-68 Steckern und 68-pol. Klemmenblock

TA900-10R

Program und Debug Box

TPIM003-10R

PIM-Modul mit 68-pin SCSI-3 Buchse

TDRV018-SW-42

VxWorks Treiber

TDRV018-SW-82

LINUX Treiber

TXMC633-FDK

FPGA Entwicklungskit