# **MVME6100** Single Board Computer

# **Installation and Use**

6806800D58D

April 2008

Ehlbeek 15a 30938 Burgwedel fon 05139-9980-0 fax 05139-9980-49

www.powerbridge.de info@powerbridge.de

© Copyright 2008 Emerson

All rights reserved.

#### **Trademarks**

Emerson, Business-Critical Continuity, Emerson Network Power and the Emerson Network Power logo are trademarks and service marks of Emerson Electric Co. © 2008 Emerson Electric Co.

All other trademarks are the property of their respective owners.

Intel® is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

PICMG<sup>®</sup>, CompactPCI<sup>®</sup>, AdvancedTCA<sup>™</sup> and the PICMG, CompactPCI and AdvancedTCA logos are registered trademarks of the PCI Industrial Computer Manufacturers Group.

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Emerson assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Emerson reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Emerson to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to a Emerson website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Emerson,

It is possible that this publication may contain reference to or information about Emerson products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Emerson intends to announce such Emerson products, programming, or services in your country.

### Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Emerson.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rightsin Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

#### Contact Address

Emerson Network Power - Embedded Computing 2900 South Diablo Way, Suite 190 Tempe, AZ 85282 USA

# **Contents**

| 1 | Hard | dware Preparation and Installation                                   |

|---|------|----------------------------------------------------------------------|

|   | 1.1  | Overview                                                             |

|   | 1.2  | Description                                                          |

|   | 1.3  | Getting Started                                                      |

|   |      | 1.3.1 Overview of Startup Procedures                                 |

|   |      | 1.3.2 Unpacking Guidelines 1                                         |

|   | 1.4  | Configuring the Hardware                                             |

|   |      | 1.4.1 SCON Header (J7)                                               |

|   |      | 1.4.2 PMC/IPMC Selection Headers (J10, J15 – J18, J25 – J28)         |

|   |      | 1.4.3 PMC I/O Voltage Configuration                                  |

|   |      | 1.4.4 Front/Rear Ethernet and Transition Module Options Header (J30) |

|   |      | 1.4.5 SROM Configuration Switch (S3)                                 |

|   |      | 1.4.6 Flash Boot Bank Select Configuration Switch (S4)               |

|   | 1.5  | Installing the Blade                                                 |

|   | 1.6  | Connecting to Peripherals                                            |

|   | 1.7  | Completing the Installation                                          |

| 2 | Star | tup and Operation                                                    |

|   | 2.1  | Introduction                                                         |

|   | 2.2  | Applying Power                                                       |

|   | 2.3  | Switches and Indicators                                              |

| 3 | MO   | ΓLoad Firmware                                                       |

|   | 3.1  | Overview                                                             |

|   | 3.2  | Implementation and Memory Requirements                               |

|   | 3.3  | MOTLoad Commands                                                     |

|   |      | 3.3.1 Utilities                                                      |

|   |      | 3.3.2 Tests                                                          |

|   |      | 3.3.3 Command List                                                   |

|   | 3.4  | Using the Command Line Interface                                     |

|   |      | 3.4.1 Command Line Rules                                             |

|   |      |                                                                      |

|   |      | 3.4.2 Command Line Help                                              |

|   | 3.5  | Firmware Settings                                                    |

|   | 3.5  | Firmware Settings                                                    |

|   | 3.5  | Firmware Settings                                                    |

|   |      | 3.5.4 Editing VME Settings                     |

|---|------|------------------------------------------------|

|   |      | 3.5.5 Deleting VME Settings                    |

|   |      | 3.5.6 Restoring Default VME Settings4          |

|   | 3.6  | Remote Start                                   |

|   | 3.7  | Alternate Boot Images and Safe Start43         |

|   | 3.8  | Firmware Startup Sequence Following Reset      |

|   | 3.9  | Firmware Scan for Boot Image                   |

|   | 3.10 | Boot Images                                    |

|   |      | 3.10.1 Checksum Algorithm                      |

|   |      | 3.10.2 Image Flags                             |

|   |      | 3.10.3 User Images                             |

|   |      | 3.10.4 Alternate Boot Data Structure           |

|   |      | 3.10.5 Alternate Boot Images and Safe Start    |

|   |      | 3.10.6 Boot Image Firmware Scan                |

|   | 3.11 | Startup Sequence                               |

|   |      |                                                |

| 4 | Func | tional Description                             |

|   | 4.4  | Overalless.                                    |

|   | 4.1  | Overview                                       |

|   | 4.2  | Features                                       |

|   | 4.3  | Block Diagram                                  |

|   | 4.4  | Processor                                      |

|   | 4.5  | L3 Cache                                       |

|   | 4.6  | System Controller                              |

|   |      | 4.6.1 CPU Bus Interface                        |

|   |      | 4.6.2 Memory Controller Interface              |

|   |      | 4.6.3 Device Controller Interface              |

|   |      | 4.6.4 PCI/PCI-X Interfaces                     |

|   |      | 4.6.5 Gigabit Ethernet MACs                    |

|   |      | 4.6.6 SRAM                                     |

|   |      | 4.6.7 General-Purpose Timers/Counters          |

|   |      | 4.6.8 Watchdog Timer                           |

|   |      | 4.6.9 I2O Message Unit                         |

|   |      | 4.6.10 Four Channel Independent DMA Controller |

|   |      |                                                |

|   |      | 4.6.12 Interrupt Controller                    |

|   | 4.7  |                                                |

|   | 4.7  | VMEbus Interface                               |

|   |      | PMCspan Interface                              |

|   | 4.9  | Flash Memory                                   |

|   | 4.10 | System Memory                                  |

|   | 4.11 | Asynchronous Serial Ports                      |

|   |      | PCI Mezzanine Card Slots                       |

|   |      | Real-Time Clock/NVRAM/Watchdog Timer           |

|   |      | IDSEL Routing                                  |

|   | 4.15 | Reset Control Logic                            |

|     |                   | Debug Support                                                                                                                                                                                                                                                                                                                                                          |                      |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 5   | Pin /             | Assignments(                                                                                                                                                                                                                                                                                                                                                           | 33                   |

|     | 5.1<br>5.2        | Overview         6           Connectors         6           5.2.1 PMC Expansion Connector (J4)         6           5.2.2 Gigabit Ethernet Connectors (J9, J93)         6           5.2.3 PCI Mezzanine Card (PMC) Connectors (J11 – J14, J21 – J24)         6                                                                                                          | 63<br>64<br>66       |

|     |                   | 5.2.4 COM1 Connector (J19) 5.2.5 VMEbus P1 Connector 5.2.6 VMEBus P2 Connector (PMC Mode) 5.2.7 VMEbus P2 Connector (IPMC Mode)                                                                                                                                                                                                                                        | 75<br>76<br>77       |

|     | 5.3               | Headers       8         5.3.1 SCON Header (J7)       8         5.3.2 Boundary Scan Header (J8)       9         5.3.3 PMC/IPMC Selection Headers (J10, J15 – J18, J25 – J28)       9         5.3.4 COM2 Header (J29)       9         5.3.5 Front/Rear Ethernet and Transition Module Options Header (J30)       9         5.3.6 Processor JTAG/COP Header (J42)       9 | 82<br>83<br>83<br>84 |

| A   | Spec              | eifications                                                                                                                                                                                                                                                                                                                                                            | 37                   |

|     | A.1<br>A.2        | Power Requirements                                                                                                                                                                                                                                                                                                                                                     | 87                   |

| С   | Rela              | ted Documentation                                                                                                                                                                                                                                                                                                                                                      | 39                   |

|     | C.1<br>C.2<br>C.3 | Emerson Network Power - Embedded Computing Documents       8         Manufacturers' Documents       8         Related Specifications       9                                                                                                                                                                                                                           | 39                   |

| В   | Ther              | mal Validation                                                                                                                                                                                                                                                                                                                                                         | <b>3</b> 3           |

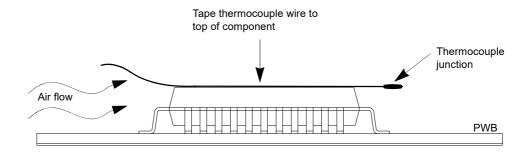

|     | B.1<br>B.2<br>B.3 | OverviewSThermally Significant ComponentsSComponent Temperature MeasurementSB.3.1 PreparationSB.3.2 Measuring Junction TemperatureSB.3.3 Measuring Case TemperatureSB.3.4 Measuring Local Air TemperatureS                                                                                                                                                             | 93<br>95<br>95<br>96 |

| Inc | lex               |                                                                                                                                                                                                                                                                                                                                                                        | 90                   |

# List of Tables

| Table 1-1  | Startup Overview                                                              | 16 |

|------------|-------------------------------------------------------------------------------|----|

| Table 1-2  | Jumper and Switch Settings                                                    | 18 |

| Table 1-3  | SROM Configuration Switch (S3)                                                | 22 |

| Table 1-4  | Configuration Switch (S4)                                                     | 24 |

| Table 1-5  | MVME6100 Connectors                                                           | 25 |

| Table 2-1  | Front-Panel LED Status Indicators                                             | 27 |

| Table 3-1  | MOTLoad Commands                                                              | 31 |

| Table 3-2  | MOTLoad Image Flags                                                           | 46 |

| Table 4-1  | MVME6100 Features Summary                                                     | 51 |

| Table 4-2  | Device Bus Parameters                                                         | 55 |

| Table 5-1  | PMC Expansion Connector (J4) Pin Assignments                                  | 64 |

| Table 5-2  | Gigabit Ethernet Connectors (J9, J93) Pin Assignment                          | 66 |

| Table 5-3  | PMC Slot 1 Connector (J11) Pin Assignments                                    | 67 |

| Table 5-4  | PMC Slot 1 Connector (J12) Pin Assignments                                    | 68 |

| Table 5-5  | PMC Slot 1 Connector (J13) Pin Assignments                                    | 69 |

| Table 5-6  | PMC Slot 1 Connector (J14) Pin Assignments                                    | 70 |

| Table 5-7  | PMC Slot 2 Connector (J21) Pin Assignments                                    | 71 |

| Table 5-8  | PMC Slot 2 Connector (J22) Pin Assignments                                    | 72 |

| Table 5-9  | PMC Slot 2 Connector (J23) Pin Assignments                                    | 73 |

| Table 5-10 | PMC Slot 2 Connector (J24) Pin Assignments                                    | 74 |

| Table 5-11 | COM1 Connector (J19) Pin Assignments                                          | 75 |

| Table 5-12 | VMEbus P1 Connector Pin Assignments                                           | 76 |

| Table 5-13 | VMEbus P2 Connector Pin Assignments (PMC Mode)                                | 77 |

| Table 5-14 | VME P2 Connector Pinouts with IPMC712                                         | 79 |

| Table 5-15 | VME P2 Connector Pinouts with IPMC761                                         | 80 |

| Table 5-16 | SCON Header (J7) Pin Assignments                                              | 82 |

| Table 5-17 | Boundary Scan Header (J8) Pin Assignments                                     | 82 |

| Table 5-18 | PMC/IPMC Configuration Jumper Block                                           | 83 |

| Table 5-19 | COM2 Planar Serial Port Header (J29) Pin Assignments                          | 83 |

| Table 5-20 | Front/Rear Ethernet and Transition Module Options Header (J30) Pin Assignment | 84 |

| Table 5-21 | Processor JTAG/COP (RISCWatch) Header (J42) Pin Assignments                   | 84 |

| Table A-1  | Power Requirements                                                            | 87 |

| Table A-2  | MVME6100 Specifications                                                       | 87 |

| Table C-1  | Emerson Network Power - Embedded Computing Documents                          | 89 |

| Table C-2  | Manufacturers' Documents                                                      | 89 |

| Table C-3  | Related Specifications                                                        | 91 |

| Table B-1  | Thermally Significant Components                                              | 93 |

# List of Figures

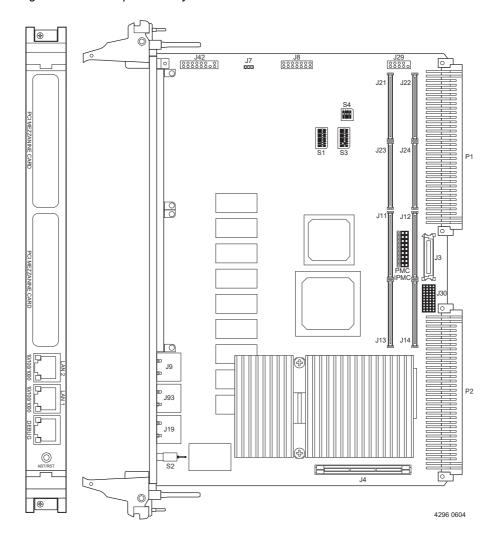

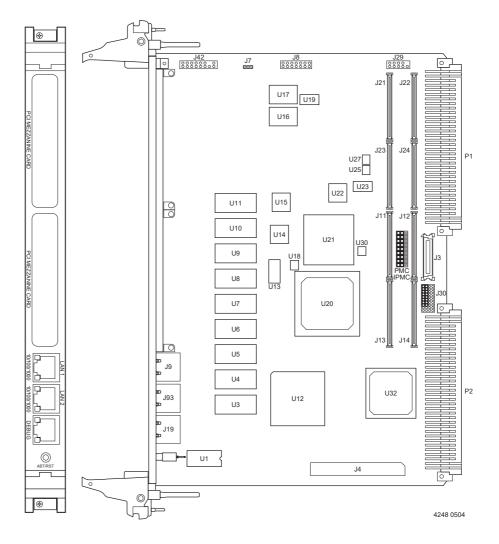

| Figure 1-1 | Component Layout                                | . 19 |

|------------|-------------------------------------------------|------|

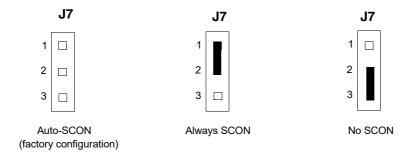

| Figure 1-2 | SCON Header Settings                            | 20   |

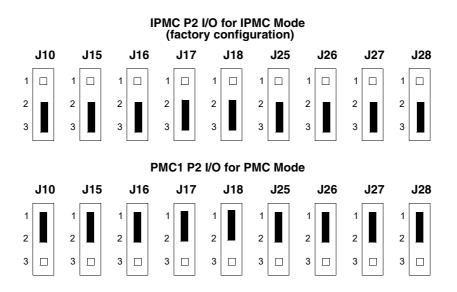

| Figure 1-3 | PMC/IPMC Header Settings                        | 20   |

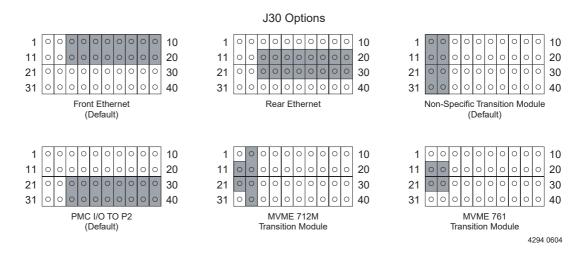

| Figure 1-4 | Front/Rear Ethernet Option Settings             | 22   |

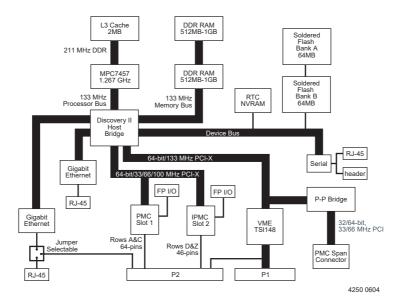

| Figure 4-1 | MVME6100 Block Diagram                          | 52   |

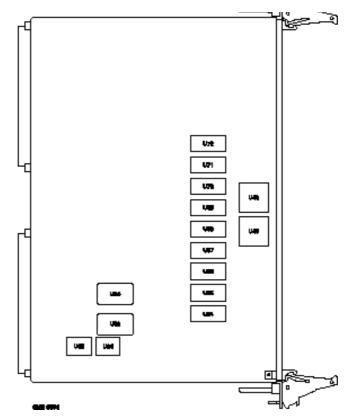

| Figure B-1 | Thermally Significant Components—Primary Side   | 94   |

| Figure B-2 | Thermally Significant Components—Secondary Side | 95   |

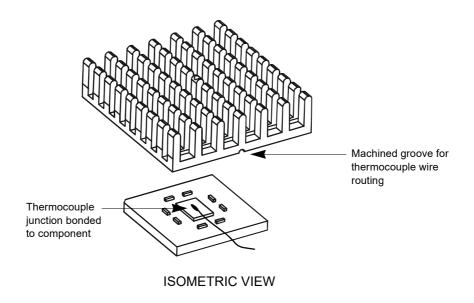

| Figure B-3 | Mounting a Thermocouple Under a Heatsink        | 97   |

Figure B-4Measuring Local Air Temperature 98

### **Overview of Contents**

This manual is divided into the following chapters and appendices:

Chapter 1, *Hardware Preparation and Installation*, provides MVME6100 board preparation and installation instructions, as well as ESD precautionary notes.

Chapter 2, Startup and Operation, provides the power-up procedure and identifies the switches and indicators on the MVMEM6100.

Chapter 3, MOTLoad Firmware, describes the basic features of the MOTLoad firmware product.

Chapter 4, Functional Description, describes the MVME6100 on a block diagram level.

Chapter 5, *Pin Assignments*, provides pin assignments for various headers and connectors on the MMVE6100 single-board computer.

Appendix A, Specifications, provides power requirements and environmental specifications.

Appendix B, *Thermal Validation*, provides information to conduct thermal evaluations and identifies thermally significant components along with their maximum allowable operating temperatures.

Appendix C, *Related Documentation*, provides a listing of related Emerson manuals, vendor documentation, and industry specifications.

The MVME61006E Series Single-Board Computer Installation and Use manual provides the information you will need to install and configure your MVME61006E single-board computer (hereinafter referred to as MVME6100). It provides specific preparation and installation information, and data applicable to the board.

As of the printing date of this manual, the MVME61006E supports the models listed below.

| Model Number    | Description                                                                |

|-----------------|----------------------------------------------------------------------------|

| MVME61006E-0161 | 1.267 GHz MPC7457 processor, 512MB DDR memory, 128MB Flash, Scanbe handles |

| MVME61006E-0163 | 1.267 GHz MPC7457 processor, 512MB DDR memory,128MB Flash, IEEE handles    |

| MVME61006E-0171 | 1.267 GHz MPC7457 processor, 1GB DDR memory, 128MB Flash, Scanbe handles   |

| MVME61006E-0173 | 1.267 GHz MPC7457 processor, 1GB DDR memory, 128MB Flash, IEEE handles     |

# **Abbreviations**

# **Conventions**

The following table describes the conventions used throughout this manual.

| Notation       | Description                                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------|

| 0x00000000     | Typical notation for hexadecimal numbers (digits are 0 through F), for example used for addresses and offsets |

| 0b0000         | Same for binary numbers (digits are 0 and 1)                                                                  |

| bold           | Used to emphasize a word                                                                                      |

| Screen         | Used for on-screen output and code related elements or commands in body text                                  |

| Courier + Bold | Used to characterize user input and to separate it from system output                                         |

| Reference      | Used for references and for table and figure descriptions                                                     |

| File > Exit    | Notation for selecting a submenu                                                                              |

| <text></text>  | Notation for variables and keys                                                                               |

| [text]         | Notation for software buttons to click on the screen and parameter description                                |

|                | Repeated item for example node 1, node 2,, node 12                                                            |

|                | Omission of information from example/command that is not necessary at the time being                          |

|                |                                                                                                               |

|                | Ranges, for example: 04 means one of the integers 0,1,2,3, and 4 (used in registers)                          |

|                | Logical OR                                                                                                    |

| Notation                                            | Description                                                                                    |  |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| ⚠ WARNING  **********************************       | Indicates a hazardous situation which, if not avoided, could result in death or serious injury |  |

| A CAUTION  SONOOCOOOCOOOCOOOCOOOCOOOCOOOCOOOCOOOCOO | Indicates a hazardous situation which, if not avoided, may result in minor or moderate injury  |  |

| NOTICE  XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX         | Indicates a property damage message                                                            |  |

| xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx              | No danger encountered. Pay attention to important information                                  |  |

# **Summary of Changes**

This is the third edition of the *Installation and Use* manual. It supersedes the November 2007 edition and incorporates the following changes.

| Part Number | Date             | Changes                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6806800D58D | April 2008       | Updated to Emerson publications style.                                                                                                                                                                                                                                                                                                                                                |

| 6806800D58C | January 2008     | Updated to remove two incorrect sources of reset. See Reset Control Logic on page 60. Table 5-13 on page 77 was updated to indicate both possible uses of pins C1, C2, C3, C4, Z25, Z27, Z29, and Z31 (when J30 is configured for rear Ethernet and when J30 is configued for full PMC mode).                                                                                         |

| 6806800D58B | November<br>2007 | Updated to better describe how to configure the VIO keying pins for the PMC sites. See <i>PMC I/O Voltage Configuration</i> on page 21. Also, Table 5-12 on page 76 was updated to identify the Geographical Addressing pins on Row D of the P1 connector and minor updates were made to correct the hot link to the literature catalog web site and update the reader comments link. |

# **Comments and Suggestions**

We welcome and appreciate your comments on our documentation. We want to know what you think about our manuals and how we can make them better.

Mail comments to us by filling out the following online form: http://www.emersonnetworkpowerembeddedcomputing.com/ > Contact Us > Online Form

In "Area of Interest" select "Technical Documentation". Be sure to include the title, part number, and revision of the manual and tell us how you used it.

### 1.1 Overview

This chapter contains the following information:

- Board preparation and installation instructions

- ESD precautionary notes

# 1.2 Description

The MVME6100 is a single-slot, single-board computer based on the MPC7457 processor, the MV64360 system controller, the Tsi148 VME Bridge ASIC, up to 1 GB of ECC-protected DDR DRAM, up to 128MB of flash memory, and a dual Gigabit Ethernet interface.

Front panel connectors on the MVME6100 board include: two RJ-45 connectors for the Gigabit Ethernet, one RJ-45 connector for the asynchronous serial port with integrated LEDs for BRDFAIL and CPU run indication, and a combined reset and abort switch.

The MVME6100 is shipped with one additional asynchronous serial port routed to an on-board header.

The MVME6100 contains two IEEE1386.1 PCI, PCI-X capable mezzanine card slots. The PMC slots are 64-bit capable and support both front and rear I/O. All I/O pins of PMC slot 1 and 46 I/O pins of PMC slot 2 are routed to the 5-row DIN, P2 connector. I/O pins 1 through 64 from J14 of PMC slot 1 are routed to row C and row A of P2. I/O pins 1 through 46 from J24 of PMC slot 2 are routed to row D and row Z of P2.

The MVME6100 has two planar PCI buses (PCI0 and PCI1). In order to support a more generic PCI bus hierarchy nomenclature, the MV64360 PCI buses will be referred to in this document as PCI bus 0 (root bridge instance 0, bus 0) and PCI bus 1 (root bridge instance 1, bus 0). PCI bus 1 connects to PMC slots 1 and 2 of the board. PCI bus 0 connects to the Tsi148 VME Bridge ASIC and PMCspan bridge (PCI6520). This interface operates at PCI-X (133 MHz) speed. Both PCI planar buses are controlled by the MV64360 system controller.

Voltage Input/Output (VIO) for PCI bus 1 is set by the location of the PMC keying pins; both pins should be set to designate the same VIO, either +3.3V or +5V.

The MVME6100 board interfaces to the VMEbus via the P1 and P2 connectors, which use 5-row 160-pin connectors as specified in the VME64 Extension Standard. It also draws +12V and +5V power from the VMEbus backplane through these two connectors. The +3.3V, +2.5V, +1.8V, and processor core supplies are regulated on-board from the +5V power.

For maximum VMEbus performance, the MVME6100 should be mounted in a VME64x compatible backplane (5-row). 2eSST transfers are not supported when a 3-row backplane is used.

The MVME6100 supports multiple modes of I/O operation. By default, the board is configured for Ethernet port 2 to the front panel (non-specific transition module), and PMC slot 1 in IPMC mode. The board can be configured to route Ethernet port 2 to P2 and support MVME712M or MVME761 transition modules. The front/rear Ethernet and transition module options are configured by jumper block J30.

Selection of PMC slot 1 in PMC or IPMC mode is done by the jumper blocks J10, J15-J18, and J25-J28 (see Table 1-2 on page 18). IPMC mode is selected when an IPMC712 or IPMC761 module is used. If an IPMC is used, J30 should be configured for the appropriate transition module (see J30 configuration options as illustrated in *Front/Rear Ethernet and Transition Module Options Header (J30)* on page 21).

The IPMC712 and IPMC761 use AD11 as the IDSEL line for the Winbond PCI-ISA bridge device. This device supplies the four serial and one parallel port of the IPMC7xx module. The Discovery II PHB (MV64360) does not recognize address lines below AD16. For this reason, although an IPMC7xx module may be used on an MVME6100, the serial and parallel ports are not available, nor addressable. This issue will be resolved at a later date.

Other functions, such as Ethernet and SCSI interfaces, are function independent of the Winbond IDSEL line. The wide SCSI interface can only be supported through IPMC connector J3.

PMC mode is backwards compatible with the MVME5100 and MVME5500 and is accomplished by configuring the on-board jumpers.

# 1.3 Getting Started

This section provides an overview of the steps necessary to install and power up the MVME6100 and a brief section on unpacking and ESD precautions.

## 1.3.1 Overview of Startup Procedures

The following table lists the things you will need to do before you can use this board and tells where to find the information you need to perform each step. Be sure to read this entire chapter, including all Caution and Warning notes, before you begin.

Table 1-1 Startup Overview

| What you need to do                                     | Refer to                               |

|---------------------------------------------------------|----------------------------------------|

| Unpack the hardware.                                    | Unpacking Guidelines on page 17        |

| Configure the hardware by setting jumpers on the board. | Configuring the Hardware on page 17    |

| Install the MVME6100 board in a chassis.                | Installing the Blade on page 24        |

| Connect any other equipment you will be using           | Connecting to Peripherals on page 25   |

| Verify the hardware is installed.                       | Completing the Installation on page 25 |

### 1.3.2 Unpacking Guidelines

Unpack the equipment from the shipping carton. Refer to the packing list and verify that all items are present. Save the packing material for storing and reshipping of equipment.

If the shipping carton is damaged upon receipt, request that the carrier's agent be present during the unpacking and inspection of the equipment.

#### **NOTICE**

Avoid touching areas of integrated circuitry; static discharge can damage circuits.

Emerson strongly recommends that you use an antistatic wrist strap and a conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules can be extremely sensitive to electrostatic discharge (ESD). After removing the component from its protective wrapper or from the system, place the component flat on a grounded, static-free surface (and, in the case of a board, component side up). Do not slide the component over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD by wearing an antistatic wrist strap (available at electronics stores) that is attached to an active electrical ground. Note that a system chassis may not be grounded if it is unplugged.

Inserting or removing modules with power applied may result in damage to module components.

#### **A WARNING**

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

## 1.4 Configuring the Hardware

This section discusses certain hardware and software tasks that may need to be performed prior to installing the board in a chassis.

To produce the desired configuration and ensure proper operation of the MVME6100, you may need to carry out certain hardware modifications before installing the module.

Most options on the MVME6100 are software configurable. Configuration changes are made by setting bits in control registers after the board is installed in a system.

Jumpers/switches are used to control those options that are not software configurable. These jumper settings are described further on in this section. If you are resetting the board jumpers from their default settings, it is important to verify that all settings are reset properly.

Figure 1-1 illustrates the placement of the jumpers, headers, connectors, switches, and various other components on the MVME6100. There are several manually configurable headers on the MVME6100 and their settings are shown in Table 1-2. Each header's default setting is enclosed in brackets. For pin assignments on the MVME6100, refer to Chapter 5, *Pin Assignments*.

Items in brackets are factory default settings.

Table 1-2 Jumper and Switch Settings

| Jumper/<br>Switch           | Function                                                                                                                         | Settings                                                                                        |                                                      |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------|

| J7                          | SCON Header                                                                                                                      | [No jumper installed]<br>1-2<br>2-3                                                             | Auto-SCON<br>Always SCON<br>No SCON                  |

| J10,<br>J15–J18,<br>J25–J28 | PMC/IPMC Selection Headers                                                                                                       | [Jumper installed]<br>1-2<br>[2-3]                                                              | PMC I/O<br>IPMC I/O for IPMC7xx<br>support (default) |

| J30                         | Front/Rear Ethernet and<br>Transition Module Options<br>Header                                                                   | Refer to Front/Rear Ethernet and Transition Module Options Header (J30) on page 21 for details. |                                                      |

| S3                          | SROM Configuration Switch,<br>sets board Geographical<br>Address                                                                 | Refer to SROM Configuration Switch (S3) on page 22 for details.                                 |                                                      |

| S4                          | Flash Boot Bank Select<br>Configuration Switch, sets<br>Write Protect A, Write Protect<br>B, Boot Bank Select, and Safe<br>Start | Refer to Flash Boot Bank Select Configuration<br>Switch (S4) on page 23 for details.            |                                                      |

The MVME6100 is factory tested and shipped with the configuration described in the following sections.

Figure 1-1 Component Layout

### 1.4.1 SCON Header (J7)

A 3-pin planar header allows the choice for auto/enable/disable SCON VME configuration. A jumper installed across pins 1 and 2 configures for SCON always enabled. A jumper installed across pins 2 and 3 configures for SCON disabled. No jumper installed configures for auto SCON.

Figure 1-2 SCON Header Settings

# 1.4.2 PMC/IPMC Selection Headers (J10, J15 – J18, J25 – J28)

Nine 3-pin planar headers are for PMC/IPMC mode I/O selection for PMC slot 1. These nine headers can also be combined into one single header block where a block shunt can be used as a jumper.

A jumper installed across pins 1 and 2 on all nine headers selects PMC1 for PMC I/O mode. A jumper across pins 2 and 3 on all nine headers selects IPMC I/O mode.

Figure 1-3 PMC/IPMC Header Settings

### 1.4.3 PMC I/O Voltage Configuration

The onboard PMC sites may be configured to support 3.3V or 5.0V I/O PMC modules. To support 3.3V or 5.0V I/O PMC modules, both PMC sites on the MVME6100 have I/O keying pins. One pin must be installed in each PMC site and both PMC sites must have their keying pins configured he same way. If both keying pins are not in the same location or if the keying pins are not installed, the PMC sites will not function. Note that setting the PMC I/O voltage to 5.0V forces the PMC sites to operate in PCI mode instead of PCI-X mode.

The VIO keying pins are the silver colored pins located either in the middle of each set of four PMC site connectors or just in front of those connectors. They serve two functions on the MVME6100: both as jumpers to select the PC lbus VIO signaling voltage for the PMC sites, and as keys to permit mounting of PMC cards that are compatible with that VIO signaling voltage (or to exclude incompatible PMC cards). In the default position in the middle of the four PMC site connectors, the signaling voltage for the PMC sites is set to 5.0V. When the keying pins are moved to the alternate location in front of their set of four PMC connectors, the signaling voltage for the PMC sites is set for 3.3V.

The keying pins for both PMC sites must be set to the same signaling voltage. Note also that the signaling voltage has an effect on the PCI bus clock speed for the PMC sites. At 5.0V signaling, the PCI bus clock speed is limited to 33 MHz, whereas 3.3V signaling voltage supports conventional PCI bus clock speeds of 33 or 66 MHz, and PCIx clock speeds of 66 or 100MHz.

A PMC card that requires 5.0V VIO only signaling has a hole in the middle of its four PMC connectors, such that it fits over the MVME6100's keying pin in that location. With the MVME6100's keying pin in the 3.3V location, that PMC card would be physically unable to be mounted. Similarly, a PMC card that requires 3.3V VIO-only signaling has its keying hole located just to the front of its four PMC connectors, and will only fit to the MVME6100 when the keying pin is located there. However, most modern PMC cards are universal with respect to the VIO signaling voltage they support, and have keying holes in both locations; that is, they will fit on the MVME6100's PMC site with the key in either location. For these PMC cards, it is recommended setting the MVME6100's keying pins to the 3.3V VIO signaling position, to allow the maximum PCIbus clock speed.

# 1.4.4 Front/Rear Ethernet and Transition Module Options Header (J30)

A 40-pin planar header allows for selecting P2 options. Jumpers installed across Row A pins 3-10 and Row B pins 3-10 enable front Ethernet access. Jumpers installed across Row B pins 3-10 and Row C pins 3-10 enable P2 (rear) Gigabit Ethernet. Only when front Ethernet is enabled can the jumpers be installed across Row C and Row D on pins 1-10 to enable P2 (rear) PMC I/O. Note that all jumpers must be installed across the same two rows (all between Row A and Row B and/or Row C and Row D, or all between Row B and Row C).

The following illustration shows jumper setting options for J30. The factory default is shown where applicable:

Figure 1-4 Front/Rear Ethernet Option Settings

Refer to Front/Rear Ethernet and Transition Module Options Header (J30) on page 84 for connector pin assignments.

### 1.4.5 SROM Configuration Switch (S3)

A part of the 8-position SMT switch, S3 enables/disables the MV64360 SROM initialization and all  $\rm I^2C$  EEPROM write protection.

The SROM Init switch is OFF to disable the MV64360 device initialization via the  $^{\circ}$ C SROM. The switch is ON to enable this sequence.

The SROM WP switch is OFF to enable write protection on all  $^{\circ}$ C. The switch is ON to disable the  $^{\circ}$ C EEPROM write protection.

Table 1-3 SROM Configuration Switch (S3)

| Position      | 2       | 1            |

|---------------|---------|--------------|

| FUNCTION      | SROM WP | SROM_INIT    |

| DEFAULT (OFF) | WP      | No SROM_INIT |

S3 position 3-8 defines the VME Geographical Address if the MVME6100 is installed in a 3-row backplane. The following is the pinout:

| Position | Function |

|----------|----------|

| 3        | VMEGAP_L |

| 4        | VMEGA4_L |

| 5        | VMEGA3_L |

| 6        | VMEGA2_L |

| 7        | VMEGA1_L |

| 8        | VMEGA0_L |

Setting the individual position to ON forces the corresponding signal to zero. If the board is installed in a 5-row backplane, the geographical address is defined by the backplane and positions 3-8 of S3 should be set to OFF. The default setting is OFF.

### 1.4.6 Flash Boot Bank Select Configuration Switch (S4)

A 4-position SMT configuration switch is located on the board to control Flash Bank B Boot block write-protect and Flash Bank A write-protect. Select the Flash Boot bank and the programmed/safe start ENV settings.

It is recommended that Bank B Write Protect always be enabled.

The Bank B Boot WP switch is OFF to indicate that the Flash Bank B Boot block is write-protected. The switch is ON to indicate no write-protection of Bank B Boot block.

The Bank A WP switch is OFF to indicate that the entire Flash Bank A is write-protected. The switch is ON to indicate no write-protection of Bank A Boot block.

When the Boot Bank Sel Switch is ON, the board boots from Bank B, when OFF, the board boots from Bank A. Default is ON (boot from Bank B).

When the Safe Start switch is set OFF, normal boot sequence should be followed by MOTLoad. When ON, MOTLoad executes Safe Start, during which the user can select the Alternate Boot Image.

Table 1-4 Configuration Switch (S4)

| Position        | 4              | 3           | 2             | 1               |

|-----------------|----------------|-------------|---------------|-----------------|

| FUNCTION        | BANK B BOOT WP | BANK A WP   | BOOT BANK SEL | SAFE START      |

| FACTORY DEFAULT | OFF<br>WP      | ON<br>No WP | ON<br>Bank B  | OFF<br>Norm ENV |

# 1.5 Installing the Blade

#### **Procedure**

Use the following steps to install the MVME6100 into your computer chassis.

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to an electrical ground (refer to *Unpacking Guidelines*). The ESD strap must be secured to your wrist and to ground throughout the procedure.

- **2.** Remove any filler panel that might fill that slot.

- 3. Install the top and bottom edge of the MVME6100 into the guides of the chassis.

### **A** CAUTION

Only use injector handles for board insertion to avoid damage/deformation to the front panel and/or PCB. Deformation of the front panel can cause an electrical short or other board malfunction.

- **4.** Ensure that the levers of the two injector/ejectors are in the outward position.

- 5. Slide the MVME6100 into the chassis until resistance is felt.

- **6.** Simultaneously move the injector/ejector levers in an inward direction.

- 7. Verify that the MVME6100 is properly seated and secure it to the chassis using the two screws located adjacent to the injector/ejector levers.

- **8.** Connect the appropriate cables to the MVME6100.

To remove the board from the chassis, press the red locking tabs (IEEE handles only) and reverse the procedure.

# 1.6 Connecting to Peripherals

When the MVME6100 is installed in a chassis, you are ready to connect peripherals and apply power to the board.

Figure 1-1 on page 19 shows the locations of the various connectors while Table 1-5 lists them for you. Refer to Chapter 5, *Pin Assignments* for the pin assignments of the connectors listed below.

Table 1-5 MVME6100 Connectors

| Connector          | Function                                  |

|--------------------|-------------------------------------------|

| J3                 | IPMC761/712 connector                     |

| J4                 | PMC expansion connector                   |

| J9, J93            | Gigabit Ethernet connectors               |

| J11, J12, J13, J14 | PCI mezzanine card (PMC) slot 1 connector |

| J19                | COM1 connector                            |

| J21, J22, J23, J24 | PCI mezzanine card (PMC) slot 2 connector |

| J29                | COM2 planar connector                     |

| P1, P2             | VME rear panel connectors                 |

# 1.7 Completing the Installation

Verify that hardware is installed and the power/peripheral cables connected are appropriate for your system configuration.

Replace the chassis or system cover, reconnect the system to the AC or DC power source, and turn the equipment power on.

### 2.1 Introduction

This chapter gives you information about the:

- Power-up procedure

- Switches and indicators

## 2.2 Applying Power

After you verify that all necessary hardware preparation is complete and all connections are made correctly, you can apply power to the system.

When you are ready to apply power to the MVME6100:

- Verify that the chassis power supply voltage setting matches the voltage present in the country of use (if the power supply in your system is not auto-sensing)

- On powering up, the MVME6100 brings up the MOTLoad prompt, MVME6100>

### 2.3 Switches and Indicators

The MVME6100 board provides a single pushbutton switch that provides both abort and reset (ABT/RST) functions. When the switch is depressed for less than three seconds, an abort interrupt is generated to the processor. If the switch is held for more than three seconds, a board hard reset is generated. The board hard reset will reset the MPC7457, MV64360, Tsi148 VME Bridge ASIC, PCI6520, PMC1/2 slots, both Ethernet PHYs, serial ports, PMCspan slot, both flash banks, and the device bus control PLD. If the MVME6100 is enabled for VME system controller, the VME bus will be reset and local reset input is sent to the Tsi148 VME controller.

The MVME6100 has two front-panel indicators:

- BDFAIL, software controlled and asserted by firmware (or other software) to indicate a configuration problem (or other failure)

- CPU, connected to a CPU bus control signal to indicate bus transfer activity

The following table describes these indicators:

Table 2-1 Front-Panel LED Status Indicators

| Function         | Label  | Color  | Description         |

|------------------|--------|--------|---------------------|

| CPU Bus Activity | CPU    | Green  | CPU bus is busy     |

| Board Fail       | BDFAIL | Yellow | Board has a failure |

**Startup and Operation**

### 3.1 Overview

The MOTLoad firmware package serves as a board power-up and initialization package, as well as a vehicle from which user applications can be booted. A secondary function of the MOTLoad firmware is to serve in some respects as a test suite providing individual tests for certain devices. This chapter includes a list of standard MOTLoad commands, the default VME and firmware settings that are changeable by the user, remote start, and the alternate boot procedure.

MOTLoad is controlled through an easy-to-use, UNIX-like, command line interface. The MOTLoad software package is similar to many end-user applications designed for the embedded market, such as the real time operating systems currently available.

Refer to the MOTLoad Firmware Package User's Manual, listed in Appendix C, Related Documentation, for more details.

# 3.2 Implementation and Memory Requirements

The implementation of MOTLoad and its memory requirements are product specific. The MVME6100 single-board computer (SBC) is offered with a wide range of memory (for example, DRAM, external cache, flash). Typically, the smallest amount of on-board DRAM that an Emerson SBC has is 32 MB. Each supported product line has its own unique MOTLoad binary image(s). Currently the largest MOTLoad compressed image is less than 1 MB in size.

## 3.3 MOTLoad Commands

MOTLoad supports two types of commands (applications): utilities and tests. Both types of commands are invoked from the MOTLoad command line in a similar fashion. Beyond that, MOTLoad utilities and MOTLoad tests are distinctly different.

#### 3.3.1 Utilities

The definition of a MOTLoad utility application is very broad. Simply stated, it is considered a MOTLoad command, if it is not a MOTLoad test. Typically, MOTLoad utility applications are applications that aid the user in some way (that is, they do something useful). From the perspective of MOTLoad, examples of utility applications are: configuration, data/status displays, data manipulation, help routines, data/status monitors, etc.

MOTLoad Firmware Tests

Operationally, MOTLoad utility applications differ from MOTLoad test applications in several ways:

Only one utility application operates at any given time (that is, multiple utility applications cannot be executing concurrently)

• Utility applications may interact with the user. Most test applications do not.

#### **3.3.2** Tests

A MOTLoad test application determines whether or not the hardware meets a given standard. Test applications are validation tests. Validation is conformance to a specification. Most MOTLoad tests are designed to directly validate the functionality of a specific SBC subsystem or component. These tests validate the operation of such SBC modules as: dynamic memory, external cache, NVRAM, real time clock, etc.

All MOTLoad tests are designed to validate functionality with minimum user interaction. Once launched, most MOTLoad tests operate automatically without any user interaction. There are a few tests where the functionality being validated requires user interaction (that is, switch tests, interactive plug-in hardware modules, etc.). Most MOTLoad test results (error-data/status-data) are logged, not printed. All MOTLoad tests/commands have complete and separate descriptions (refer to the MOTLoad Firmware Package User's Manual for this information).

All devices that are available to MOTLoad for validation/verification testing are represented by a unique device path string. Most MOTLoad tests require the operator to specify a test device at the MOTLoad command line when invoking the test.

A listing of all device path strings can be displayed through the **devShow** command. If an SBC device does not have a device path string, it is not supported by MOTLoad and can not be directly tested. There are a few exceptions to the device path string requirement, like testing RAM, which is not considered a true device and can be directly tested without a device path string. Refer to the **devShow** command description page in the MOTLoad Firmware Package User's Manual.

Most MOTLoad tests can be organized to execute as a group of related tests (a testSuite) through the use of the testSuite command. The expert operator can customize their testing by defining and creating a custom testSuite(s). The list of built-in and user-defined MOTLoad testSuites, and their test contents, can be obtained by entering testSuite -d at the MOTLoad prompt. All testSuites that are included as part of a product specific MOTLoad firmware package are product specific. For more information, refer to the testSuite command description page in the MOTLoad Firmware Package User's Manual.

Test results and test status are obtained through the testStatus, errorDisplay, and taskActive commands. Refer to the appropriate command description page in the MOTLoad Firmware Package User's Manual for more information.

Command List MOTLoad Firmware

### 3.3.3 Command List

The following table provides a list of all current MOTLoad commands. Products supported by MOTLoad may or may not employ the full command set. Typing help at the MOTLoad command prompt will display all commands supported by MOTLoad for a given product.

Table 3-1 MOTLoad Commands

| Command    | Description                                             |

|------------|---------------------------------------------------------|

| as         | One-Line Instruction Assembler                          |

| bcb        | Block Compare Byte/Halfword/Word                        |

| bch        |                                                         |

| bcw        |                                                         |

| bdTempShow | Display Current Board Temperature                       |

| bfb        | Block Fill Byte/Halfword/Word                           |

| bfh        |                                                         |

| bfw        |                                                         |

| blkCp      | Block Copy                                              |

| blkFmt     | Block Format                                            |

| blkRd      | Block Read                                              |

| blkShow    | Block Show Device Configuration Data                    |

| blkVe      | Block Verify                                            |

| blkWr      | Block Write                                             |

| bmb        | Block Move Byte/Halfword/Word                           |

| bmh        |                                                         |

| bmw        |                                                         |

| br         | Assign/Delete/Display User-Program Break-Points         |

| bsb        | Block Search Byte/Halfword/Word                         |

| bsh        |                                                         |

| bsw        |                                                         |

| bvb        | Block Verify Byte/Halfword/Word                         |

| bvh        |                                                         |

| bvw        |                                                         |

| cdDir      | ISO9660 File System Directory Listing                   |

| cdGet      | ISO9660 File System File Load                           |

| clear      | Clear the Specified Status/History Table(s)             |

| cm         | Turns on Concurrent Mode                                |

| csb        | Calculates a Checksum Specified by Command-line Options |

| csh        |                                                         |

| CSW        |                                                         |

| devShow    | Display (Show) Device/Node Table                        |

| diskBoot   | Disk Boot (Direct-Access Mass-Storage Device)           |

MOTLoad Firmware Command List

Table 3-1 MOTLoad Commands (continued)

| Command      | Description                                                |

|--------------|------------------------------------------------------------|

| downLoad     | Down Load S-Record from Host                               |

| ds           | One-Line Instruction Disassembler                          |

| echo         | Echo a Line of Text                                        |

| elfLoader    | ELF Object File Loader                                     |

| errorDisplay | Display the Contents of the Test Error Status Table        |

| eval         | Evaluate Expression                                        |

| execProgram  | Execute Program                                            |

| fatDir       | FAT File System Directory Listing                          |

| fatGet       | FAT File System File Load                                  |

| fdShow       | Display (Show) File Discriptor                             |

| flashLock    | Flash Memory Sector Lock                                   |

| flashProgram | Flash Memory Program                                       |

| flashShow    | Display Flash Memory Device Configuration Data             |

| flashUnlock  | Flash Memory Sector Unlock                                 |

| gd           | Go Execute User-Program Direct (Ignore Break-Points)       |

| gevDelete    | Global Environment Variable Delete                         |

| gevDump      | Global Environment Variable(s) Dump (NVRAM Header + Data)  |

| gevEdit      | Global Environment Variable Edit                           |

| gevInit      | Global Environment Variable Area Initialize (NVRAM Header) |

| gevList      | Global Environment Variable Labels (Names) Listing         |

| gevShow      | Global Environment Variable Show                           |

| gn           | Go Execute User-Program to Next Instruction                |

| go           | Go Execute User-Program                                    |

| gt           | Go Execute User-Program to Temporary Break-Point           |

| hbd          | Display History Buffer                                     |

| hbx          | Execute History Buffer Entry                               |

| help         | Display Command/Test Help Strings                          |

| I2CacheShow  | Display state of L2 Cache and L2CR register contents       |

| l3CacheShow  | Display state of L3 Cache and L3CR register contents       |

| mdb          | Memory Display Bytes/Halfwords/Words                       |

| mdh          |                                                            |

| mdw          |                                                            |

| memShow      | Display Memory Allocation                                  |

| mmb          | Memory Modify Bytes/Halfwords/Words                        |

| mmh<br>mmw   |                                                            |

| 111111144    |                                                            |

Command List MOTLoad Firmware

Table 3-1 MOTLoad Commands (continued)

| Command          | Description                                      |

|------------------|--------------------------------------------------|

| mpuFork          | Execute program from idle processor              |

| mpuShow          | Display multi-processor control structure        |

| mpuStart         | Start the other MPU                              |

| netBoot          | Network Boot (BOOT/TFTP)                         |

| netShow          | Display Network Interface Configuration Data     |

| netShut          | Disable (Shutdown) Network Interface             |

| netStats         | Display Network Interface Statistics Data        |

| noCm             | Turns off Concurrent Mode                        |

| pciDataRd        | Read PCI Device Configuration Header Register    |

| pciDataWr        | Write PCI Device Configuration Header Register   |

| pciDump          | Dump PCI Device Configuration Header Register    |

| pciShow          | Display PCI Device Configuration Header Register |

| pciSpace         | Display PCI Device Address Space Allocation      |

| ping             | Ping Network Host                                |

| portSet          | Port Set                                         |

| portShow         | Display Port Device Configuration Data           |

| rd               | User Program Register Display                    |

| reset            | Reset System                                     |

| rs               | User Program Register Set                        |

| set              | Set Date and Time                                |

| sromRead         | SROM Read                                        |

| sromWrite        | SROM Write                                       |

| sta              | Symbol Table Attach                              |

| stl              | Symbol Table Lookup                              |

| stop             | Stop Date and Time (Power-Save Mode)             |

| taskActive       | Display the Contents of the Active Task Table    |

| tc               | Trace (Single-Step) User Program                 |

| td               | Trace (Single-Step) User Program to Address      |

| testDisk         | Test Disk                                        |

| testEnetPtP      | Ethernet Point-to-Point                          |

| testNvramRd      | NVRAM Read                                       |

| testNvramRdWr    | NVRAM Read/Write (Destructive)                   |

| testRam          | RAM Test (Directory)                             |

| testRamAddr      | RAM Addressing                                   |

| testRamAlt       | RAM Alternating                                  |

| testRamBitToggle | RAM Bit Toggle                                   |

| 1                |                                                  |

Table 3-1 MOTLoad Commands (continued)

| Command           | Description                                         |

|-------------------|-----------------------------------------------------|

| testRamBounce     | RAM Bounce                                          |

| testRamCodeCopy   | RAM Code Copy and Execute                           |

| testRamEccMonitor | Monitor for ECC Errors                              |

| testRamMarch      | RAM March                                           |

| testRamPatterns   | RAM Patterns                                        |

| testRamPerm       | RAM Permutations                                    |

| testRamQuick      | RAM Quick                                           |

| testRamRandom     | RAM Random Data Patterns                            |

| testRtcAlarm      | RTC Alarm                                           |

| testRtcReset      | RTC Reset                                           |

| testRtcRollOver   | RTC Rollover                                        |

| testRtcTick       | RTC Tick                                            |

| testSerialExtLoop | Serial External Loopback                            |

| testSerialIntLoop | Serial Internal Loopback                            |

| testStatus        | Display the Contents of the Test Status Table       |

| testSuite         | Execute Test Suite                                  |

| testSuiteMake     | Make (Create) Test Suite                            |

| testWatchdogTimer | Tests the Accuracy of the Watchdog Timer Device     |

| tftpGet           | TFTP Get                                            |

| tftpPut           | TFTP Put                                            |

| time              | Display Date and Time                               |

| transparentMode   | Transparent Mode (Connect to Host)                  |

| tsShow            | Display Task Status                                 |

| upLoad            | Up Load Binary Data from Target                     |

| version           | Display Version String(s)                           |

| vmeCfg            | Manages user specified VME configuration parameters |

| vpdDisplay        | VPD Display                                         |

| vpdEdit           | VPD Edit                                            |

| wait              | Wait for Test Completion                            |

| waitProbe         | Wait for I/O Probe to Complete                      |

# 3.4 Using the Command Line Interface

Interaction with MOTLoad is performed via a command line interface through a serial port on the SBC, which is connected to a terminal or terminal emulator (for example, Window's Hypercomm). The default MOTLoad serial port settings are: 9600 baud, 8 bits, no parity.

The MOTLoad command line interface is similar to a UNIX command line shell interface. Commands are initiated by entering a valid MOTLoad command (a text string) at the MOTLoad command line prompt and pressing the carriage-return key to signify the end of input. MOTLoad then performs the specified action. An example of a MOTLoad command line prompt is shown below. The MOTLoad prompt changes according to what product it is used on (for example, MVME5500, MVME6100).

#### Example:

MVME6100>

If an invalid MOTLoad command is entered at the MOTLoad command line prompt, MOTLoad displays a message that the command was not found.

#### Example:

```

MVME6100> mytest

"mytest" not found

MVME6100>

```

If the user enters a partial MOTLoad command string that can be resolved to a unique valid MOTLoad command and presses the carriage-return key, the command will be executed as if the entire command string had been entered. This feature is a user-input shortcut that minimizes the required amount of command line input. MOTLoad is an ever changing firmware package, so user-input shortcuts may change as command additions are made.

#### Example:

```

MVME6100> version

```

```

Copyright: Motorola Inc.1999-2002, All Rights Reserved MOTLoad RTOS Version 2.0 PAL Version 0.1 (Motorola MVME6100)

```

#### Example:

```

MVME6100> ver

```

```

Copyright: Motorola Inc. 1999-2002, All Rights Reserved MOTLoad RTOS Version 2.0 PAL Version 0.1 (Motorola MVME6100)

```

If the partial command string cannot be resolved to a single unique command, MOTLoad will inform the user that the command was ambiguous.

#### Example:

```

MVME6100> te

"te" ambiguous

MVME6100>

```

MOTLoad Firmware Command Line Rules

#### 3.4.1 Command Line Rules

There are a few things to remember when entering a MOTLoad command:

- Multiple commands are permitted on a single command line, provided they are separated by a single semicolon (;)

- Spaces separate the various fields on the command line (command/arguments/options)

- The argument/option identifier character is always preceded by a hyphen (-) character

- Options are identified by a single character

- Option arguments immediately follow (no spaces) the option

- All commands, command options, and device tree strings are case sensitive

#### Example:

```

MVME6100> flashProgram -d/dev/flash0 -n00100000

```

For more information on MOTLoad operation and function, refer to the MOTLoad Firmware Package User's Manual.

### 3.4.2 Command Line Help

Each MOTLoad firmware package has an extensive, product-specific help facility that can be accessed through the **help** command. The user can enter **help** at the MOTLoad command line to display a complete listing of all available tests and utilities.

#### Example

```

MVME6100> help

```

For help with a specific test or utility the user can enter the following at the MOTLoad prompt:

```

help <command name>

```

The **help** command also supports a limited form of pattern matching. Refer to the **help** command page.

#### Example

#### MVME6100> help testRam

```

Usage: testRam [-aPh] [-bPh] [-iPd] [-nPh] [-tPd] [-v]

Description: RAM Test [Directory]

Argument/Option Description

-a Ph: Address to Start (Default = Dynamic Allocation)

-b Ph: Block Size (Default = 16KB)

-i Pd: Iterations (Default = 1)

-n Ph: Number of Bytes (Default = 1MB)

-t Ph: Time Delay Between Blocks in OS Ticks (Default = 1)

-v O : Verbose Output

MVME6100>

```

Firmware Settings MOTLoad Firmware

# 3.5 Firmware Settings

The following sections provide additional information pertaining to the VME firmware settings of the MVME6100. A few VME settings are controlled by hardware jumpers while the majority of the VME settings are managed by the firmware command utility vmeCfg.

#### 3.5.1 Default VME Settings

As shipped from the factory, the MVME6100 has the following VME configuration programmed via Global Environment Variables (GEVs) for the Tsi148 VME controller. The firmware allows certain VME settings to be changed in order for the user to customize the environment. The following is a description of the default VME settings that are changeable by the user. For more information, refer to the MOTLoad User's Manual and Tundra's Tsi148 User Manual, listed in Appendix C, Related Documentation.

• MVME6100> vmeCfg -s -m

```

Displaying the selected Default VME Setting - interpreted as follows:

VME PCI Master Enable [Y/N] = Y

MVME6100>

```

The PCI Master is enabled.

MVME6100> vmeCfg -s -r234

```

Displaying the selected Default VME Setting - interpreted as follows:

VMEbus Master Control Register = 00000003

MVME6100>

```

The VMEbus Master Control Register is set to the default (RESET) condition.

● MVME6100> vmeCfg -s -r238

```

Displaying the selected Default VME Setting

- interpreted as follows:

VMEbus Control Register = 000000008

MVME6100>

```

The VMEbus Control Register is set to a Global Timeout of 2048 µseconds.

MVME6100 > vmeCfg -s -r414

```

Displaying the selected Default VME Setting

- interpreted as follows:

CRG Attribute Register = 00000000

CRG Base Address Upper Register = 00000000

CRG Base Address Lower Register = 00000000

MVME6100>

```

The CRG Attribute Register is set to the default (RESET) condition.

MVME6100> vmeCfg -s -i0

MOTLoad Firmware Default VME Settings

```

Displaying the selected Default VME Setting

- interpreted as follows:

Inbound Image 0 Attribute Register = 000227AF

Inbound Image 0 Starting Address Upper Register = 00000000

Inbound Image 0 Starting Address Lower Register = 00000000

Inbound Image 0 Ending Address Upper Register = 00000000

Inbound Image 0 Ending Address Lower Register = 1FFF0000

Inbound Image 0 Translation Offset Upper Register = 00000000

Inbound Image 0 Translation Offset Lower Register = 00000000

MVME6100>

```

Inbound window 0 (ITAT0) is not enabled; Virtual FIFO at 256 bytes, 2eSST timing at SST320, respond to 2eSST, 2eVME, MBLT, and BLT cycles, A32 address space, respond to Supervisor, User, Program, and Data cycles. Image maps from 0x00000000 to 0x1FFF0000 on the VMbus, translates 1x1 to the PCI-X bus (thus 1x1 to local memory). To enable this window, set bit 31 of ITAT0 to 1.

For Inbound Translations, the Upper Translation Offset Register needs to be set to 0xFFFFFFF to ensure proper translations to the PCI-X Local Bus.

● MVME6100> vmeCfg -s -o1

```

Displaying the selected Default VME Setting

- interpreted as follows:

Outbound Image 1 Attribute Register = 80001462

Outbound Image 1 Starting Address Upper Register = 00000000

Outbound Image 1 Starting Address Lower Register = 91000000

Outbound Image 1 Ending Address Upper Register = 00000000

Outbound Image 1 Ending Address Lower Register = AFFF0000

Outbound Image 1 Translation Offset Upper Register = 00000000

Outbound Image 1 Translation Offset Lower Register = 70000000

Outbound Image 1 ZeSST Broadcast Select Register = 00000000

```

Outbound window 1 (OTAT1) is enabled, 2eSST timing at SST320, transfer mode of 2eSST, A32/D32 Supervisory access. The window accepts transfers on the PCI-X Local Bus from 0x91000000-0xAFFF0000 and translates them onto the VMEbus using an offset of 0x70000000, thus an access to 0x91000000 on the PCI-X Local Bus becomes an access to 0x01000000 on the VMEbus.

● MVME6100 > vmeCfg -s -o2

```

Displaying the selected Default VME Setting

- interpreted as follows:

Outbound Image 2 Attribute Register = 80001061

Outbound Image 2 Starting Address Upper Register = 00000000

Outbound Image 2 Starting Address Lower Register = B0000000

Outbound Image 2 Ending Address Upper Register = 00000000

Outbound Image 2 Ending Address Lower Register = B0FF0000

```

Default VME Settings MOTLoad Firmware

```

Outbound Image 2 Translation Offset Upper Register = 00000000

Outbound Image 2 Translation Offset Lower Register = 40000000

Outbound Image 2 2eSST Broadcast Select Register = 00000000

MVME6100>

```

Outbound window 2 (OTAT2) is enabled, 2eSST timing at SST320, transfer mode of SCT, A24/D32 Supervisory access. The window accepts transfers on the PCI-X Local Bus from 0xB0000000-0xB0FF0000 and translates them onto the VMEbus using an offset of 0x40000000, thus an access to 0xB0000000 on the PCI-X Local Bus becomes an access to 0xF0000000 on the VMEbus.

#### ● MVME6100> vmeCfg -s -o3

```

Displaying the selected Default VME Setting

- interpreted as follows:

Outbound Image 3 Attribute Register = 80001061

Outbound Image 3 Starting Address Upper Register = 00000000

Outbound Image 3 Starting Address Lower Register = B3FF0000

Outbound Image 3 Ending Address Upper Register = 00000000

Outbound Image 3 Ending Address Lower Register = B3FF0000

Outbound Image 3 Translation Offset Upper Register = 00000000

Outbound Image 3 Translation Offset Lower Register = 4C000000

Outbound Image 3 ZeSST Broadcast Select Register = 00000000

```

Outbound window 3 (OTAT3) is enabled, 2eSST timing at SST320, transfer mode of SCT, A16/D32 Supervisory access. The window accepts transfers on the PCI-X Local Bus from 0xB3FF0000-0xB3FF0000 and translates them onto the VMEbus using an offset of 0x4C000000, thus an access to 0xB3FF0000 on the PCI-X Local Bus becomes an access to 0xFFFF0000 on the VMEbus.

#### ● MVME6100> vmeCfg -s -o7

```

Displaying the selected Default VME Setting

- interpreted as follows:

Outbound Image 7 Attribute Register = 80001065

Outbound Image 7 Starting Address Upper Register = 00000000

Outbound Image 7 Starting Address Lower Register = B1000000

Outbound Image 7 Ending Address Upper Register = 00000000

Outbound Image 7 Ending Address Lower Register = B1FF0000

Outbound Image 7 Translation Offset Upper Register = 00000000

Outbound Image 7 Translation Offset Lower Register = 4F000000

Outbound Image 7 Zesst Broadcast Select Register = 00000000

```

Outbound window 7 (OTAT7) is enabled, 2eSST timing at SST320, transfer mode of SCT, CR/CSR Supervisory access. The window accepts transfers on the PCI-X Local Bus from 0xB1000000-0xB1FF0000 and translates them onto the VMEbus using an offset of 0x4F000000, thus an access to 0xB1000000 on the PCI-X Local Bus becomes an access to 0x00000000 on the VMEbus.

### 3.5.2 Control Register/Control Status Register Settings

The CR/CSR base address is initialized to the appropriate setting based on the Geographical address; that is, the VME slot number. See the VME64 Specification and the VME64 Extensions for details. As a result, a 512K byte CR/CSR area can be accessed from the VMEbus using the CR/CSR AM code.

### 3.5.3 Displaying VME Settings

To display the changeable VME setting, type the following at the firmware prompt:

- vmeCfg -s -m

Displays Master Enable state

- vmeCfg -s -i(0 7)

Displays selected Inbound Window state

- vmeCfg -s -o(0 7)

Displays selected Outbound Window state

- vmeCfg -s -r184

Displays PCI Miscellaneous Register state

- vmeCfg -s -r188

Displays Special PCI Target Image Register state

- vmeCfg -s -r400

Displays Master Control Register state

- vmeCfg -s -r404

Displays Miscellaneous Control Register state

- vmeCfg -s -r40C

Displays User AM Codes Register state

- vmeCfg -s -rF70

Displays VMEbus Register Access Image Control Register state

## 3.5.4 Editing VME Settings

To edit the changeable VME setting, type the following at the firmware prompt:

- vmeCfg -e -m

Edits Master Enable state

- vmeCfg -e -i(0 7)

Edits selected Inbound Window state

- vmeCfg -e -o(0 7)

Edits selected Outbound Window state

- vmeCfg -e -r184

Edits PCI Miscellaneous Register state

- vmeCfg -e -r188

Edits Special PCI Target Image Register state