The Embedded I/O Company

# TAMC532 32 x 12/14 Bit 50/75 Msps ADC for MTCA.4 Rear-I/O

#### Application Information

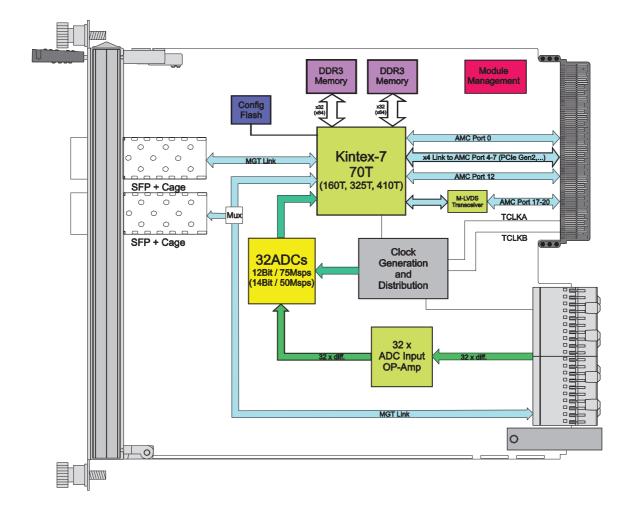

The TAMC532 is an Advanced Mezzanine Card (AMC) according to MTCA.4 (MicroTCA Enhancements for Rear I/O and Precision Timing). 32 analog input channels allow sampling of analog signals with 75 Msps at 12 Bit resolution (optional 50 Msps at 14 Bit).

The TAMC532 utilizes Back-IO via Zone 3 to interface the ADCs with the signal conditioning located on the  $\mu$ RTM. This modular concept allows adapting the TAMC532 to nearly any analog input requirement without changing the AMC itself.

A very powerful on-board clocking structure enables using the TAMC532 in nearly all kind of clocking scenarios. A self-clocked application as well as synchronizing multiple TAMC532 is possible, allowing applications with up to several hundred simultaneous sampled channels.

Data readout can be done via several interfaces like e.g. PCI-Express or two SFP-cages in the front panel.

The on-board DRR3 memory can be used for data buffering in triggered applications that require subsequent readout. Assuming sufficient data fabric bandwidth, the DDR3 memory can also be used as double buffer, allowing infinite data acquisition.

Up to eight backplane triggers are available, each configurable as input or output.

The TAMC532 is equipped with a powerful Kintex-7 FPGA for data preprocessing and transfer. By default, the Kintex-7 FPGA is configured with a firmware that provides a very functional readout system and full control over the numerous clocking and trigger options. It can also be adapted to customer needs if necessary.

In-circuit programming and debugging of the FPGA design (e.g. using Xilinx "ChipScope") is supported. The Program and Debug Box TA900 or the standard Xilinx JTAG header allows access to the module while it is inserted in a system. In addition to the module's JTAG Chain, the TA900 allows access to the UART of the on-board Module Management Controller (MMC) and to two user pins of the FPGA. If a UART core is implemented in the FPGA, serial communication via the TA900 is possible.

The TA900 can be accessed by USB 2.0 and by a 14-pin JTAG Header (e.g. for connecting a Xilinx Platform Cable).

Ehlbeek 15a 30938 Burgwedel fon 05139-9980-0 fax 05139-9980-49

www.powerbridge.de info@powerbridge.de

Issue 1.1.0

2021-09-28

TEWS TECHNOLOGIES GmbH keeps the right to change technical specification without further notice. All trademarks mentioned are property of their respective owners.

TEWS TECHNOLOGIES GmbHAm Bahnhof 725469 Halstenbek, GermanyPhone: +49 (0) 4101 4058 0Fax: +49 (0) 4101 4058 19e-mail: info@tews.comwww.tews.com

### **Technical Information**

- O Form Factor: PICMG MTCA.4 module

- O Board size: 180.6 mm x 146.5 mm

- O Double-width / Mid-Size

- O Fabric Interconnects

- Gigabit Ethernet on AMC Port 0

- O x4 PCIe Gen 2 Link (AMC.1 Type 4 compliant)

- O AMC Port 12

- O x1 Link to µRTM

- O 2 x SFP+ Cage

- O TCLK A and B support

- O M-LVDS Transceivers on AMC ports 17-20

- O Kintex-7 70T FPGA

- O Integrated PCIe Gen 2 Endpoint Block

- Multi-Gigabit transceiver with up to 6.6Gb/sec Dual FPGA Configuration Flash

- 2x DDR3 memory

- O 32 bit data bus width each

- O 256 MByte each

- O Low Jitter Clock distribution and generation

- **O** 32 x ADC

- 12 Bit at 75 Msps (TAMC532-10R)

- O 14 Bit at 50 Msps (TAMC532-11R)

- O ±1V differential analog inputs via Zone 3

- O IPMI V1.5 support

- O Front Panel LEDs:

- O Blue Hot-Swap LED

- O Red Fail LED

- O Green User LED

- O MTCA.4 Zone 3 Interface according to Class A2.1

- O Operating Temperature: 0°C to +70°C

TEWS TECHNOLOGIES GmbH keeps the right to change technical specification without further notice. All trademarks mentioned are property of their respective owners.

## TEWS TECHNOLOGIES GmbH

## The Embedded I/O Company

## **Order Information**

## **RoHS Compliant**

**TAMC532-10R** Kintex-7 70T, 2 x 256 MByte at 32 Bit DDR3, 32 x 12 Bit 75 Msps ADC TAMC532-11R Kintex-7 70T, 2 x 256 MByte at 32 Bit DDR3, 32 x 14 Bit 50 Msps ADC

## Optional available on request:

- Operating temperature -40°C to +85°C

- Faster FPGA speed grades

- Other FPGA logic densities:

- Kintex-7 160T 0

- Kintex-7 325T 0

- Kintex-7 410T 0

- Memory options:

0

- Kintex-7 70T: 0

- 2 x 512 MByte at 32 Bit / 2 x 1 GByte at 32 Bit Kintex-7 160T / 325T / 410T: 2 x 1 GByte at 64 Bit / 2 x 2 GByte at 64 Bit

- For the availability of non-RoHS compliant (leaded solder) products please contact TEWS.

#### **Documentation** TAMC532-DOC

User Manual

#### **Software**

TAMC532-SW-25 Integrity Software Support TAMC532-SW-42 VxWorks Software Support TAMC532-SW-65 Windows Software Support TAMC532-SW-82 Linux Software Support QNX Software Support TAMC532-SW-95

For other operating systems please contact TEWS.

**Related Products** TAMC532-TM-10R µRTM for TAMC532 Accessories

TA900-10R

Program and Debug Box, USB, JTAG, 20pin FPC connector, including USB A-USB B and FPC Flexcable

TEWS TECHNOLOGIES GmbH keeps the right to change technical specification without further notice. All trademarks mentioned are property of their respective owners.

Issue 1.1.0 2021-09-28