# **TAMC532**

# 32 x 12/14 Bit 50/75 Msps ADC for MTCA.4 Rear-I/O

Version 1.1

### **User Manual**

Issue 1.1.0 September 2021

#### **TAMC532-10R**

32 x 12 Bit 75 Msps ADC for MTCA.4 Rear-I/O

#### **TAMC532-11R**

32 x 14 Bit 50 Msps ADC for MTCA.4 Rear-I/O

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP\_RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

©2015-2021 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

# **Document History**

| Issue | Description                                                                                                                                                                                                                                                                                                                                                                                                                              | Date         |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1.0.0 | Initial Issue                                                                                                                                                                                                                                                                                                                                                                                                                            | April 2015   |

| 1.0.1 | <ul> <li>Changed PCIe Bar Endianness in Chapter 6.1.1</li> <li>Added DMA Descriptor Big Endian Model Note in Chapter 6.1.4</li> <li>Added information about auto-load sequence abort in chapter 5.2.1.2</li> <li>Modified I2C Bridge Status Register Information concerning Write and Read Data FIFO Counter</li> <li>Added register address information to the register description tables throughout the document.</li> </ul>          | April 2015   |

| 1.0.2 | <ul> <li>Added CSPT Data Endian Model mode in CSPT Unit [x] Control Register</li> <li>Changed Bit Positions of WRS_SWR_DCNT and WRS_SRD_DCNT in I2C Bridge Control Register</li> <li>Corrected the register names at offset 0x02 and 0x03 in Table 6-41</li> <li>Removed minor typo (Lower / Upper) in chapter 6.2.2.4 and 6.2.2.5</li> </ul>                                                                                            | May 2015     |

| 1.0.3 | <ul> <li>Added Information about minimum ADC sample Clock Frequency of 10MHz</li> <li>Added Information about reset time after ADC sampling frequency change.</li> <li>Added note about trigger edge sensitivity in CSPT Unit [x] Control Register</li> <li>Added description about triggers in chapter ADC Data Acquisition</li> <li>Updated Chapter "LED Indicators"</li> <li>Added DCIRST_LOCKED in Module Status Register</li> </ul> | July 2015    |

| 1.0.4 | - BCC:                                                                                                                                                                                                                                                                                                                                                                                                                                   | January 2016 |

| Issue | Description                                                                                                                                                                                                                 | Date              |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1.1.0 | Functional extension to V1.1 due to new FPGA firmware and general review of the document                                                                                                                                    | September<br>2021 |

|       | <ul> <li>Automatic Buffer Termination Disable functionality added in the CSPT<br/>Unit Control Register</li> </ul>                                                                                                          |                   |

|       | <ul> <li>Software controlled Buffer Termination added in the Application<br/>Command Register</li> </ul>                                                                                                                    |                   |

|       | <ul> <li>Typo corrected in the title of the FPGA JTAG Connector Pin<br/>Assignment Table.</li> </ul>                                                                                                                        |                   |

|       | <ul> <li>Typo correction in the description of the BCCs Si5338 Status Register<br/>and LMK_SCI of LMK04816 Status register: the description for value<br/>0 and 1 was interchanged</li> </ul>                               |                   |

|       | <ul> <li>Clarification in the description of the BCCs Miscellaneous Register:<br/>reserved state added to FPGA_IN0 and FPGA_IN1</li> </ul>                                                                                  |                   |

|       | <ul> <li>Correction of the Affected analog input paths of DIS_AMP_B in the<br/>BCCs ADC Input Amplifiers Control Register</li> </ul>                                                                                        |                   |

|       | <ul> <li>All phrases related to the user-programmability of the FPGA are<br/>removed throughout the document. This better matches the fact that<br/>the TAMC532 is delivered with a factory programmed firmware.</li> </ul> |                   |

|       | - Description of LEDs 1-4 revised and User Mode added                                                                                                                                                                       |                   |

|       | <ul> <li>Jitter Attenuator Control Register removed from BCC, as the jitter<br/>attenuator has been removed.</li> </ul>                                                                                                     |                   |

|       | - Description of BCC Firmware Identification Register added                                                                                                                                                                 |                   |

|       | <ul> <li>Added note for CSPT Unit memory interface synchronization requirement in chapter Application Control Register</li> </ul>                                                                                           |                   |

|       | - Revised DDR3 Memory usage description in chapter 5.4                                                                                                                                                                      |                   |

# **Table of Contents**

| 1 | PRODUCT DESCRIPTION                      | 11 |

|---|------------------------------------------|----|

| 2 | TECHNICAL SPECIFICATION                  | 12 |

| 3 | HANDLING AND OPERATING INSTRUCTIONS      | 13 |

|   | 3.1 ESD Protection                       |    |

|   | 3.2 Thermal Considerations               |    |

|   | 3.3 I/O Signaling Voltages               |    |

| 4 | IPMI SUPPORT                             |    |

| • | 4.1 Temperature and Voltage Sensors      |    |

|   | 4.2 FRU Information                      |    |

|   | 4.2.1 Board Info Area                    |    |

|   | 4.2.2 Product Info Area                  |    |

|   | 4.2.3 Multi Record Area                  |    |

|   | 4.2.3.1 Module Current Requirements      |    |

|   | 4.2.3.2 AMC Point-to-Point Connectivity  |    |

|   | 4.2.3.3 Clock Configuration              |    |

| 5 | FUNCTIONAL DESCRIPTION                   |    |

| J |                                          | _  |

|   | 5.1 Overview                             |    |

|   | 5.2 FPGA                                 |    |

|   | 5.2.1 Interrupt Handling                 |    |

|   | 5.2.3 ADC Data Acquisition               |    |

|   | 5.2.4 I2C Bridge                         | 23 |

|   | 5.3 Board Configuration Controller (BCC) |    |

|   | 5.4 DDR3 Memory                          |    |

|   | 5.5 Fabric Interfaces                    |    |

|   | 5.5.1 PCI-Express                        |    |

|   | 5.6 Flash Memory                         |    |

|   | 5.7 ADC Clocking                         |    |

|   | 5.7.1 Crosspoint Switch                  |    |

|   | 5.7.3 VCXO                               |    |

|   | 5.7.4 ADCs                               | 28 |

|   | 5.7.5 TCLKB                              |    |

|   | 5.7.6 AMC_TCLK                           |    |

|   | 5.7.7 AMC_CLRU                           |    |

|   | 5.9 Analog Inputs                        |    |

|   | 5.9.1 ADC Sample Clock                   |    |

|   | 5.9.2 Input Voltage Range                |    |

|   | 5.10 Debug                               |    |

|   | 5.10.1 LEDs                              |    |

|   | 5.10.2 UART                              |    |

|   | 5.10.3 JTAG                              |    |

|   | 5.12 µRTM Detection                      |    |

| 6 | ADDRESSABLE RESOURCES                    |    |

| O |                                          |    |

|   | 6.1 FPGA                                 | 32 |

|   |                                          |    |

| 6.1.1                | Structural Description                                   |          |

|----------------------|----------------------------------------------------------|----------|

| 6.1.2                | PCIe Configuration                                       |          |

| 6.1.3                | Register Interface                                       |          |

| 6.1.3.1              | Module Control Register (0x00)                           |          |

| 6.1.3.2              | Module Status Register (0x04)                            |          |

| 6.1.3.3              | Module Interrupt Enable Register (0x08)                  |          |

| 6.1.3.4              | Module Interrupt Status Register (0x0C)                  |          |

| 6.1.3.5              | ADC Channel [xx] Data Register                           |          |

| 6.1.3.6              | I2C Bridge Control Register (0x50)                       |          |

| 6.1.3.7              | I2C Bridge Clock Divider Register (0x54)                 |          |

| 6.1.3.8              | I2C Bridge Status Register (0x58)                        |          |

| 6.1.3.9              | I2C Bridge Command Register (0x5C)                       | 48       |

| 6.1.3.10             |                                                          |          |

| 6.1.3.11             | <b>5</b>                                                 |          |

| 6.1.3.12             |                                                          |          |

| 6.1.3.13             |                                                          |          |

| 6.1.3.14             |                                                          |          |

| 6.1.3.15             |                                                          |          |

| 6.1.3.16             |                                                          |          |

| 6.1.3.17             |                                                          |          |

| 6.1.3.18             |                                                          | 50       |

| 6.1.3.19             |                                                          | 50       |

| 6.1.3.20             |                                                          |          |

| 6.1.3.21<br>6.1.3.22 | · · · · · · · · · · · · · · · · · · ·                    |          |

| 6.1.4                | DMA Descriptors                                          |          |

| 6.1.4.1              | DMA Descriptor Control DW.                               |          |

| 6.1.4.2              | ·                                                        |          |

| 6.1.4.3              | DMA Descriptor Data Memory Address                       |          |

| 6.1.4.4              | Reserved                                                 |          |

|                      | rd Configuration Controller (BCC)                        | 62       |

| 6.2.1                | BCC-I2C                                                  |          |

| 6.2.1.1              | LMK04816 Status Register (0x00)                          |          |

| 6.2.1.2              | SI5338 Status Register (0x01)                            |          |

| 6.2.1.3              | AMC Rx/Tx Differential Pair [x] Control Register         | 65       |

| 6.2.1.4              | SFP Control Register (0x06)                              |          |

| 6.2.1.5              | SPI Control Register (0x07)                              |          |

| 6.2.1.6              | Miscellaneous Register (0x09)                            |          |

| 6.2.1.7              | Configuration DIP Switches Register (0x0A)               |          |

| 6.2.1.8              | ADC Input Amplifiers Control Register (0x0B)             |          |

| 6.2.1.9              | Frequency Adjustment Control Register (0x0C)             |          |

| 6.2.1.10             | BCC Firmware Identification Register (0xFC)              | 72       |

| 6.2.2                | Configuration-I2C                                        |          |

| 6.2.2.1              | BCC Bridge Register Space                                | 73       |

| 6.2.2.2              | ADC Setup Interface Control Register (0x00)              | 74       |

| 6.2.2.3              | ADC Setup Interface Status Register (0x01)               |          |

| 6.2.2.4              | ADC Setup Interface Lower Target Address Register (0x02) | 75       |

| 6.2.2.5              | ADC Setup Interface Upper Target Address Register (0x03) |          |

| 6.2.2.6              | ADC Setup Interface Read Data (0x04)                     | 76       |

| 6.2.2.7              | ADC Setup Interface Write Data (0x05)                    | 76       |

| 6.2.2.8              | LMK Setup Interface Control Register (0x10)              | 76       |

| 6.2.2.9              | LMK Setup Interface Status Register (0x11)               |          |

| 6.2.2.10             | •                                                        |          |

| 6.2.2.11             | LMK Write Data Register [x]                              | 70       |

|                      |                                                          |          |

| 6.2.2.12             | CPS Setup Interface Control Register (0x20)              | 79       |

|                      | CPS Setup Interface Control Register (0x20)              | 79<br>79 |

|    |       |       | CPS Setup Interface Write Data (0x23) |    |

|----|-------|-------|---------------------------------------|----|

| 7  | BOA   | ARD C | ONFIGURATION                          | 82 |

|    | 7.1   |       | riew                                  |    |

|    | 7.2   |       | 3 Keying Pin                          |    |

|    | 7.3   |       | witch                                 |    |

| 8  | INST  | ΓALLA | ATION                                 | 84 |

|    | 8.1   | AMC I | Module Installation                   | 84 |

|    | 8.1   |       | nsertion                              |    |

|    | 8.1   |       | extraction                            |    |

|    | 8.2   | μRTM  | Module Installation                   | 85 |

|    | 8.2   |       | RTM Insertion                         |    |

|    | 8.2   | .2 µ  | IRTM Extraction                       | 85 |

| 9  | LED   | INDIC | CATORS                                | 86 |

| 10 | 1/0 ( | CONN  | ECTORS                                | 89 |

|    | 10.1  | Overv | riew                                  | 89 |

|    | 10.2  | Zone  | 3 Connectors                          | 90 |

|    | 10.   | 2.1 J | 30                                    | 90 |

|    |       |       | 31                                    |    |

|    |       |       | Connectors                            |    |

|    | 10.4  |       | JTAG Connector                        |    |

|    | 10.5  | Debug | g Connector                           | 93 |

|    | 10.6  | AMC ( | Connector                             | 94 |

|    | 10.7  | MMC   | Header                                | 95 |

# **List of Tables**

| TABLE 2-1: TECHNICAL SPECIFICATION                                     | 12 |

|------------------------------------------------------------------------|----|

| TABLE 4-1: TEMPERATURE AND VOLTAGE SENSORS                             | 14 |

| TABLE 4-2: FRU INFORMATION                                             | 14 |

| TABLE 4-3: BOARD INFO AREA                                             | 15 |

| TABLE 4-4: PRODUCT INFO AREA                                           | 15 |

| TABLE 4-5: MODULE CURRENT REQUIREMENTS                                 | 15 |

| TABLE 4-6: AMC POINT-TO-POINT CONNECTIVITY                             | 16 |

| TABLE 4-7: CLOCK CONFIGURATION                                         | 17 |

| TABLE 5-1: MAXIMUM SAMPLE COUNT PER CHANNEL                            | 21 |

| TABLE 5-2: ADC DATA ALIGNMENT                                          | 22 |

| TABLE 6-1: PCIE CONFIGURATION REGISTERS                                | 33 |

| TABLE 6-2: PCIE BAR OVERVIEW                                           | 33 |

| TABLE 6-3: MODULE REGISTER SPACE                                       | 36 |

| TABLE 6-4: MODULE CONTROL REGISTER (0X00)                              | 36 |

| TABLE 6-5: MODULE STATUS REGISTER (0X04)                               | 38 |

| TABLE 6-6: MODULE INTERRUPT ENABLE REGISTER (0X08)                     | 41 |

| TABLE 6-7: MODULE INTERRUPT STATUS REGISTER (0X0C)                     | 44 |

| TABLE 6-8: ADC CHANNEL [XX] DATA REGISTER                              | 44 |

| TABLE 6-9: I2C BRIDGE CONTROL REGISTER (0X50)                          | 46 |

| TABLE 6-10: I2C BRIDGE CLOCK DIVIDER REGISTER (0X54)                   | 46 |

| TABLE 6-11: I2C BRIDGE STATUS REGISTER (0X58)                          | 48 |

| TABLE 6-12: I2C BRIDGE COMMAND REGISTER (0X5C)                         | 49 |

| TABLE 6-13: I2C BRIDGE WRITE DATA FIFO INTERFACE REGISTER (0X60)       | 49 |

| TABLE 6-14: I2C BRIDGE READ FIFO DATA REGISTER (0X64)                  | 49 |

| TABLE 6-15: DMA CONTROLLER [X] CONTROL REGISTER                        | 50 |

| TABLE 6-16: DMA CONTROLLER [X] STATUS REGISTER                         | 51 |

| TABLE 6-17: DMA CONTROLLER [X] BASE DESCRIPTOR ADDRESS REGISTER        | 51 |

| TABLE 6-18: DMA CONTROLLER [X] CURRENT DESCRIPTOR ADDRESS REGISTER     | 52 |

| TABLE 6-19: APPLICATION CONTROL REGISTER (0X100)                       | 53 |

| TABLE 6-20: CSPT UNIT [X] CONTROL REGISTER                             | 55 |

| TABLE 6-21: CSPT UNIT [X] DATA REGISTER #0 – PRE-TRIGGER SAMPLE COUNT  | 56 |

| TABLE 6-22: CSPT UNIT [X] DATA REGISTER #1 – POST-TRIGGER SAMPLE COUNT | 56 |

| TABLE 6-23: APPLICATION STATUS REGISTER (0X160)                        | 57 |

| TABLE 6-24: APPLICATION COMMAND REGISTER (0X164)                       | 58 |

| TABLE 6-25: FIRMWARE IDENTIFICATION REGISTER (0X1FC)                   | 59 |

| TABLE 6-26 : DMA DESCRIPTOR CONTROL DW                                 |    |

| TABLE 6-27: DMA DESCRIPTOR NEXT DESCRIPTOR ADDRESS                     | 61 |

| TABLE 6-28: DMA DESCRIPTOR DATA MEMORY ADDRESS                         | 61 |

| TABLE 6-29: RESERVED                                                   | 61 |

| TABLE 6-30 : BCC TARGET REGISTER SPACE                                 | 62 |

| TABLE 6-31: LMK04816 STATUS REGISTER (0X00)                            | 63 |

|                                                                        |    |

| TABLE 6-32: SI5338 STATUS REGISTER (0X01)                            | 64 |

|----------------------------------------------------------------------|----|

| TABLE 6-33: AMC RX/TX DIFFERENTIAL PAIR [X] CONTROL REGISTER         |    |

| TABLE 6-34: SFP CONTROL REGISTER (0X06)                              | 66 |

| TABLE 6-35: SPI CONTROL REGISTER (0X07)                              | 67 |

| TABLE 6-37: MISCELLANEOUS REGISTER (0X09)                            | 68 |

| TABLE 6-38: CONFIGURATION DIP SWITCHES REGISTER (0X0A)               | 69 |

| TABLE 6-39: ADC INPUT AMPLIFIERS CONTROL REGISTER (0X0B)             | 71 |

| TABLE 6-40: FREQUENCY ADJUSTMENT CONTROL REGISTER (0X0C)             | 72 |

| TABLE 6-41: BCC FIRMWARE IDENTIFICATION REGISTER (0XFC)              | 72 |

| TABLE 6-42: BCC BRIDGE REGISTER SPACE                                |    |

| TABLE 6-43: ADC SETUP INTERFACE CONTROL REGISTER (0X00)              | 74 |

| TABLE 6-44: ADC SETUP INTERFACE STATUS REGISTER (0X01)               | 75 |

| TABLE 6-45: ADC SETUP INTERFACE LOWER TARGET ADDRESS REGISTER (0X02) | 75 |

| TABLE 6-46: ADC SETUP INTERFACE UPPER TARGET ADDRESS REGISTER (0X03) | 75 |

| TABLE 6-47: ADC SETUP INTERFACE READ DATA (0X04)                     | 76 |

| TABLE 6-48: ADC SETUP INTERFACE WRITE DATA (0X05)                    | 76 |

| TABLE 6-49: LMK SETUP INTERFACE CONTROL REGISTER (0X10)              | 76 |

| TABLE 6-50: LMK SETUP INTERFACE STATUS REGISTER (0X11)               | 77 |

| TABLE 6-51: LMK READ REGISTER [X]                                    | 77 |

| TABLE 6-52: LMK WRITE REGISTER [X]                                   | 78 |

| TABLE 6-53: CPS SETUP INTERFACE CONTROL REGISTER (0X20)              | 79 |

| TABLE 6-54: CPS SETUP INTERFACE READ DATA (0X21)                     | 79 |

| TABLE 6-55: CPS SETUP INTERFACE READ DATA (0X22)                     | 80 |

| TABLE 6-56: CPS SETUP INTERFACE WRITE DATA (0X23)                    |    |

| TABLE 7-1: ZONE 3 KEYING PIN                                         | 82 |

| TABLE 7-2: DIP-SWITCH                                                | 83 |

| TABLE 9-1: BASIC MICROTCA LEDS                                       |    |

| TABLE 9-2: BOARD STATUS LEDS                                         |    |

| TABLE 9-3: FRONT PANEL LEDS 1-4 (BCC CONTROLLED)                     |    |

| TABLE 9-4: FRONT PANEL LEDS 1-4 (STATUS MODE)                        | 88 |

| TABLE 10-1: ZONE 3 J30 CONNECTOR PIN ASSIGNMENT                      | 90 |

| TABLE 10-2: ZONE 3 J31 CONNECTOR PIN ASSIGNMENT                      | 90 |

| TABLE 10-3: SFP+ CONNECTOR PIN ASSIGNMENT                            | 91 |

| TABLE 10-4: FPGA JTAG CONNECTOR PIN ASSIGNMENT                       | 92 |

| TABLE 10-5: DEBUG CONNECTOR PIN ASSIGNMENT                           | 93 |

| TABLE 10-6: AMC CONNECTOR PIN ASSIGNMENT                             |    |

| TABLE 10-7 : MMC HEADER PIN ASSIGNMENT FACTORY USE ONLY              | 95 |

# **List of Figures**

| FIGURE 1-1:  | BLOCK DIAGRAM                                   | .11 |

|--------------|-------------------------------------------------|-----|

| FIGURE 5-1 : | FUNCTIONAL BLOCK DIAGRAM                        | .18 |

| FIGURE 5-2 : | DDR3 MEMORY INTERFACES                          | .25 |

| FIGURE 5-3 : | FABRIC INTERFACES                               | .25 |

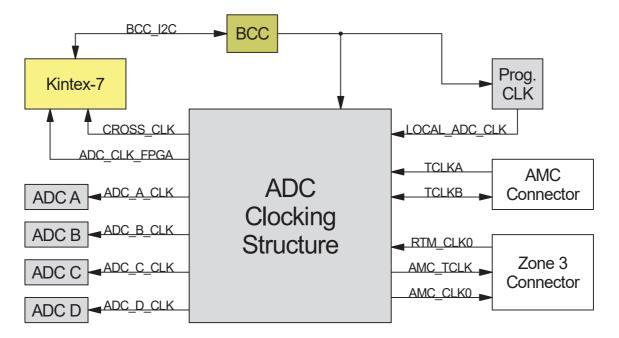

| FIGURE 5-4:  | ADC CLOCKING OVERVIEW                           | .26 |

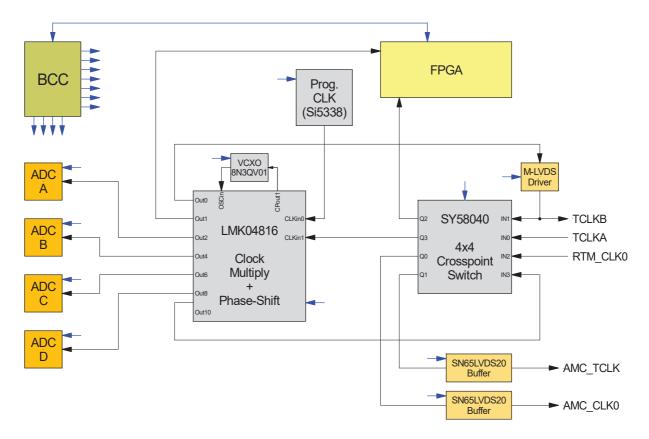

| FIGURE 5-5 : | ADC CLOCK GENERATION AND DISTRIBUTION STRUCTURE | .27 |

| FIGURE 5-6 : | M-LVDS I/O                                      | .29 |

|              | SINGLE ANALOG INPUT                             |     |

|              | 8 X ANALOG INPUT GROUP                          |     |

| FIGURE 6-1:  | TAMC532 FIRMWARE SOC STRUCTURE                  | .32 |

| FIGURE 7-1:  | BOARD CONFIGURATION OVERVIEW                    | .82 |

| FIGURE 8-1 : | HOT-SWAP STATES                                 | .84 |

| FIGURE 9-1 : | FRONT PANEL LED VIEW                            | .86 |

| FIGURE 10-1  | · CONNECTOR OVERVIEW                            | 89  |

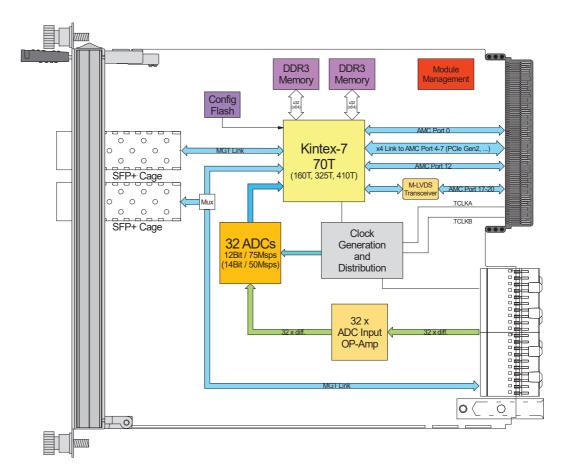

# 1 Product Description

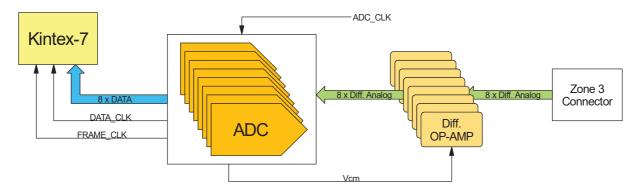

The TAMC532 is an Advanced Mezzanine Card (AMC) according to MTCA.4 (MicroTCA Enhancements for Rear I/O and Precision Timing). 32 analog input channels allow sampling of analog signals with 75 Msps at 12 Bit resolution (optional 50 Msps at 14 Bit).

The TAMC532 utilizes Back-IO via Zone 3 to interface the ADCs with the signal conditioning located on the  $\mu$ RTM. This modular concept allows adapting the TAMC532 to nearly any analog input requirement without changing the AMC itself.

A very powerful on-board clocking structure enables using the TAMC532 in nearly all kind of clocking scenarios. A self-clocked application as well as synchronizing multiple TAMC532 is possible, allowing applications with up to several hundred simultaneous sampled channels.

Data readout is done via PCI-Express.

The on-board DRR3 memory is used for data buffering in triggered applications that require subsequent readout.

Up to eight backplane triggers are available, each configurable as input or output.

The TAMC532 is equipped with a powerful Kintex-7 FPGA for data acquisition and transfer. The Kintex-7 FPGA is configured with a firmware that provides a very functional readout system and full control over the numerous clocking and trigger options.

Operating temperature range is -0°C to +70°C.

Figure 1-1: Block Diagram

# 2 Technical Specification

| AMC Interface                                              |                                                                                                                                 |                                                                                                |  |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| Advanced Mezzanine Card (AMC) Interface conforming to      |                                                                                                                                 |                                                                                                |  |  |

| Mechanical Interface                                       | PICMG® AMC.0 R2.0 (Advanced Mezzanine Card Base Specification)                                                                  |                                                                                                |  |  |

| moonamour morrado                                          | Module Type: Double Mid-size Module                                                                                             |                                                                                                |  |  |

|                                                            | AMC Port 4-7                                                                                                                    |                                                                                                |  |  |

| Electrical Interfaces                                      | AMC Port 17-20 via M-LVDS Transceivers                                                                                          |                                                                                                |  |  |

|                                                            | TCLKA + B                                                                                                                       |                                                                                                |  |  |

| IPMI Support                                               |                                                                                                                                 |                                                                                                |  |  |

| IPMI Version                                               | 1.5                                                                                                                             |                                                                                                |  |  |

|                                                            | Blue Hot-Swa                                                                                                                    | p LED                                                                                          |  |  |

| Front Panel LEDs                                           |                                                                                                                                 | ndication LED (LED1)                                                                           |  |  |

|                                                            | Green Board OK / User LED (LED2)                                                                                                |                                                                                                |  |  |

| Main On-Board Devices                                      |                                                                                                                                 |                                                                                                |  |  |

| FPGA                                                       | XC7K70T-1FBG676C or compatible                                                                                                  |                                                                                                |  |  |

| DDR3 Memory                                                | MT41J64M16LA or compatible                                                                                                      |                                                                                                |  |  |

| Flash                                                      | N25Q256 or compatible                                                                                                           |                                                                                                |  |  |

| ADC                                                        | TAMC532-10R : AD9637 (12 Bit resolution)                                                                                        |                                                                                                |  |  |

| ADC                                                        | TAMC532-11R : AD9257 (14 Bit resolution)                                                                                        |                                                                                                |  |  |

| Zone 3 I/O Interface                                       |                                                                                                                                 |                                                                                                |  |  |

| Analog Input Voltage                                       | 0V ±1V (differential)                                                                                                           |                                                                                                |  |  |

| Number of Channels                                         | ber of Channels 32                                                                                                              |                                                                                                |  |  |

| I/O Connector 2 x 30pair ADF Connector according to MTCA.4 |                                                                                                                                 | F Connector according to MTCA.4                                                                |  |  |

| Physical Data                                              |                                                                                                                                 |                                                                                                |  |  |

|                                                            | Management Power: 70mA typical @ +3.3V DC                                                                                       |                                                                                                |  |  |

| Power Requirements                                         | Payload Power: 2A typical @ +12V DC                                                                                             |                                                                                                |  |  |

|                                                            | max. Current                                                                                                                    | Draw as per Module Current Requirements Record: 5A                                             |  |  |

| Tomporatura Banga                                          | Operating                                                                                                                       | 0 °C to +70 °C                                                                                 |  |  |

| Temperature Range                                          | Storage                                                                                                                         | 0 °C to +70 °C                                                                                 |  |  |

|                                                            | 272000 h                                                                                                                        |                                                                                                |  |  |

|                                                            |                                                                                                                                 | own are based on calculation according to MIL-HDBK-217F and Notice 2; Environment: $G_B$ 20°C. |  |  |

| MTBF                                                       |                                                                                                                                 | lation is based on component FIT rates provided by the component                               |  |  |

|                                                            | suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation. |                                                                                                |  |  |

| Humidity                                                   | 5 – 95 % non-condensing                                                                                                         |                                                                                                |  |  |

| Weight                                                     | 385 g                                                                                                                           | 5                                                                                              |  |  |

|                                                            | 1300 9                                                                                                                          |                                                                                                |  |  |

Table 2-1: Technical Specification

# 3 Handling and Operating Instructions

### 3.1 ESD Protection

The AMC module is sensitive to static electricity. Packing, unpacking and all other module handling has to be done in an ESD/EOS protected Area.

### 3.2 Thermal Considerations

Forced air cooling is recommended during operation. Without forced air cooling, damage to the device can occur.

# 3.3 I/O Signaling Voltages

The FPGA I/O-Lines to the  $\mu$ RTM are directly connected to the FPGA I/O pins. The I/O voltage of these FPGA I/O pins is 2.5V maximum.

The FPGA I/O pins are NOT 3.3V or 5V tolerant.

# 4 IPMI Support

The AMC module provides a Module Management Controller (MMC) that performs health monitoring, hot-swap functionality and stores the Field Replaceable Unit (FRU) information. The MMC communicates via an Intelligent Platform Management Interface (IPMI).

# 4.1 Temperature and Voltage Sensors

The MMC monitors on-board sensors and signals sensor events to the superordinated IPMI controller / shelf manager. Available sensors are listed in the table below.

| Sensor Number | Signal Type | Thresholds              | Signal Monitored |

|---------------|-------------|-------------------------|------------------|

| 0             | Event       | -                       | Hot-swap switch  |

| 1             | Temperature | Inr lcr Inc unc ucr unr | Board Temp.      |

| 2             |             | Inr lcr Inc unc ucr unr | RAM Temp.        |

| 3             | Temperature | Inr lcr Inc unc ucr unr | FPGA Temp.       |

| 4             | Voltage     | Inr Icr Inc unc ucr unr | +12V (PWR)       |

| 5             | Voltage     | Inr lcr Inc unc ucr unr | +1V0             |

| 6             | Voltage     | Inr lcr Inc unc ucr unr | +1V5             |

| 7             | Voltage     | Inr lcr Inc unc ucr unr | +1V8             |

unr: upper non-recoverable, ucr: upper critical, unc: upper non-critical lnr: lower non-recoverable, lcr: lower critical, lnc: lower non-critical

Table 4-1: Temperature and Voltage Sensors

### 4.2 FRU Information

The MMC stores the module FRU information in a non-volatile EEPROM. Some of the records are writeable. If records are modified, the user is responsible for setting the proper checksums. The actual FRU information data is shown below.

| Area                            | Size (in Bytes) | Writeable |

|---------------------------------|-----------------|-----------|

| Common Header                   | 8               | no        |

| Chassis Info Area               | 0               | no        |

| Board Info Area                 | variable        | no        |

| Product Info Area               | variable        | no        |

| Multi Record Area               |                 |           |

| Module Current Requirements     | variable        | yes       |

| AMC Point-to-Point Connectivity | variable        | yes       |

| Clock Configuration             | variable        | yes       |

| Compatibility Record            | variable        | yes       |

Table 4-2: FRU Information

#### 4.2.1 Board Info Area

| Product Information    | Value                                         |

|------------------------|-----------------------------------------------|

| Version                | 1                                             |

| Language Code          | 0x00 - english                                |

| Manufacturer date/time | determined at manufacturing                   |

| Board manufacturer     | TEWS TECHNOLOGIES GmbH                        |

| Board product name     | TAMC532                                       |

| Board serial number    | determined at manufacturing (see board label) |

| Board part number      | TAMC532-xxR<br>-xx = -10 / -11                |

Table 4-3: Board Info Area

#### 4.2.2 Product Info Area

| Product Information     | Value                                         |

|-------------------------|-----------------------------------------------|

| Version                 | 1                                             |

| Language Code           | 0x00 - english                                |

| Product manufacturer    | TEWS TECHNOLOGIES GmbH                        |

| Product name            | TAMC532                                       |

| Board part/model number | TAMC532-xxR<br>-xx = -10 / -11                |

| Product version         | V1.0 Rev. A (see board label)                 |

| Product serial number   | determined at manufacturing (see board label) |

| Asset tag               | = Product serial Number                       |

Table 4-4: Product Info Area

#### 4.2.3 Multi Record Area

#### 4.2.3.1 Module Current Requirements

The "Current Draw" value holds the Payload Power (PWR) requirement of the AMC given as current requirement in units of 0.1A at 12V. The table below shows the factory default "Current Draw" value for this AMC module.

| Product Information | Value      |

|---------------------|------------|

| Current Draw        | 0x32 (5 A) |

Table 4-5: Module Current Requirements

The AMC's MMC announces the current demand to the shelf manager. If the power budget for the AMC slot is smaller than this value, the shelf manager may not enable Payload power for the used slot.

### 4.2.3.2 AMC Point-to-Point Connectivity

The AMC module provides the following AMC Point-to-Point Connectivity Record Data.

| Channel | Port | Link Type            | Link Type Extension           | Link Grouping ID    | Asymmetric Match            |

|---------|------|----------------------|-------------------------------|---------------------|-----------------------------|

| 0       | 0    | AMC.2 Ethernet       | 1000BASE-BX<br>Ethernet Link  | Single Channel Link | Exact match                 |

|         |      | AMC.1 PCI<br>Express | Gen 1 PCI Express, non-SSC    | Single Channel Link | PCI Express<br>Primary Port |

| 4       | 4    | AMC.1 PCI<br>Express | Gen 1 PCI Express,<br>SSC     | Single Channel Link | PCI Express<br>Primary Port |

| 1       | 4    | AMC.1 PCI<br>Express | Gen 2 PCI Express,<br>non-SSC | Single Channel Link | PCI Express<br>Primary Port |

|         |      | AMC.1 PCI<br>Express | Gen 2 PCI Express,<br>SSC     | Single Channel Link | PCI Express<br>Primary Port |

|         | 4.7  | AMC.1 PCI<br>Express | Gen 1 PCI Express, non-SSC    | Single Channel Link | PCI Express<br>Primary Port |

|         |      | AMC.1 PCI<br>Express | Gen 1 PCI Express,<br>SSC     | Single Channel Link | PCI Express<br>Primary Port |

| 2       | 4-7  | AMC.1 PCI<br>Express | Gen 2 PCI Express,<br>non-SSC | Single Channel Link | PCI Express<br>Primary Port |

|         |      | AMC.1 PCI<br>Express | Gen 2 PCI Express,<br>SSC     | Single Channel Link | PCI Express<br>Primary Port |

Table 4-6: AMC Point-to-Point Connectivity

#### 4.2.3.3 Clock Configuration

AMC FCLKA (CLK3) is used as the PCI Express Reference Clock.

| Clock ID | Clock Features                        | Clock Family | Clock Accuracy    | Clock Frequency |

|----------|---------------------------------------|--------------|-------------------|-----------------|

| FCLKA    | Clock Receiver, connected through PLL | PCI Express  | PCI Express Gen 1 | 100 MHz nom.    |

| FOLKA    | Clock Receiver, connected through PLL | PCI Express  | PCI Express Gen 2 | 100 MHz nom.    |

| TCLKA    | Clock Receiver, connected through PLL | undefined    | undefined         | 10kHz – 500MHz  |

|          | Clock Receiver, connected without PLL | Undefined    | Undefined         | 10MHz – 50MHz   |

|          | Clock Receiver, connected through PLL | Undefined    | Undefined         | 10kHz – 500MHz  |

| TCLKB    | Clock Receiver, connected without PLL | Undefined    | Undefined         | 10MHz – 400MHz  |

|          | Clock Source with PLL                 | undefined    | undefined         | 10kHz – 100MHz  |

Table 4-7: Clock Configuration

# 4.2.4 Modifying FRU Records

Some of the records are writeable to allow adaption to certain systems. If records are modified, the user is responsible for setting the proper checksums.

# 5 Functional Description

This chapter gives an overview of the various functions of the TAMC532.

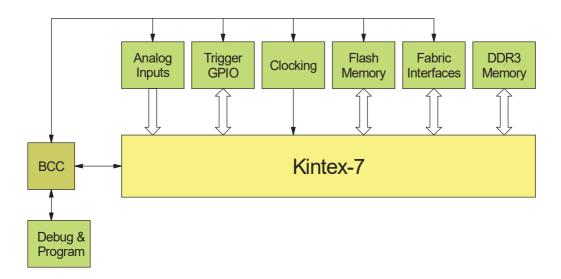

### 5.1 Overview

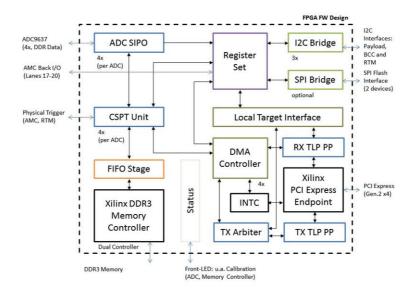

From a FPGA centric view, the TAMC532 can be divided into several functional blocks. The following subchapters provide a detailed description for each of these blocks.

Figure 5-1: Functional Block Diagram

### 5.2 FPGA

The heart of the TAMC532 is the Kintex-7 FPGA. It is configured with a firmware that provides a very functional readout system and control over the numerous clocking and trigger options.

### 5.2.1 Interrupt Handling

The firmware contains different functions or sub-components. For a simplified interrupt handling, the interrupt-relevant information of these components has been grouped within the Module Interrupt Status Register.

Interrupts are controlled via a two-stage technique: a Module Interrupt Global Enable Bit and separate Interrupt Source Enable Bits.

Different interrupt event information is registered within the Module Interrupt Status Register. Every interrupt source has a corresponding enable bit within the Module Interrupt Enable Register. When a specific interrupt occurs and if this specific interrupt is enabled, it is registered as Interrupt Status Register information.

Consequently, interrupts that are not enabled cannot be registered/captured within the Interrupt Status Register and got lost.

Bits inside the Interrupt Status Register can be cleared (Interrupt Acknowledge) by active-high bit writing (W1C). If a bit indicates a logical one it will be zero after such a write. If a bit indicates a logical zero it will remain at logical zero after such a write, meaning that it cannot be set by software.

The content of the Interrupt Status Register does not generate PCIe Interrupts without any control. If the Global Module Interrupt Enable Bit is not set, PCIe Interrupts are prohibited. In such a case, the Interrupt Status Register also operates as Interrupt Pending Register.

In accordance with PCIe requirements, legacy and MSI interrupt generation is supported. MSI-X is not supported.

In case of legacy interrupts, INTA interrupts are generated. In case of MSI interrupts, only a single vector will be used. Configuring MSI-X will cause that no interrupts are generated.

The module interrupt configuration usage information can be obtained via the Module Status Register.

#### 5.2.2 DMA Controller

The design contains four different DMA Controllers *DMACs*, which operate and behave in the same way. Every DMA Controller has a separate register set to obtain status information and write control settings.

As long as a DMAC is not enabled, its logic is held in reset state and all status information is at default.

Besides, every DMAC provides a self-clearing SW reset to reset the logic and status information (instead of toggling the corresponding enable off and on).

After a DMAC is enabled (DMAC\_EN), the controller performs an auto-load sequence of the Descriptor Information stored at the host memory address indicated by the Base Descriptor Address Register. The load sequence is aborted if the DMA Base Address Register is 0x00000000.

Consequently, the Base Descriptor Address Register should point to a valid Descriptor Address before enabling the DMA Controller.

Descriptor linked list reading continues until the last read DMA Descriptor does not provide an successor element (Next Descriptor Address is 0x00000000), the last descriptor has the EOL bit set or the internal descriptor queue buffer is full (256 elements pre-fetched).

The Descriptor Queue is filled successively; one after the other, meaning that one DMA descriptor is requested at a time (for internal handling of outstanding request).

Every request statically reads the first 3 DWs from the specified (host) memory address (via Base Descriptor Address Register or Next Descriptor Address). There is no sanity check on the read information. It is expected that the read information is in accordance with the specified DMA Descriptor Structure.

For future improvements every DMA Descriptor should consider the 4th reserved DW.

The current internal descriptor queue memory fill-level can be obtained by reading the corresponding DMA Controller status register (DMAC\_DQ\_SIZE).

A load sequence can also be initiated by writing into the Base Descriptor Address Register after the DMAC is enabled and if the internal buffer descriptor memory is not full (Descriptor Queue Size is 0xFF). The loaded Descriptor information is queued after the last Descriptor stored within the internal buffer.

The Base descriptor Address Register should not be write-accessed during auto-prefetching operations since this would initiate false Descriptor order.

Some more corresponding information is provided within the status register.

If an error occurs during reading descriptor information, bit DMAC\_DQH\_ECR is set. Conditions that cause such an error are: PCle timeout, returned read length does not match the requested one or an erroneous completion is reported by the system.

The current descriptor host memory buffer size (DMAC\_RDB\_SIZE) is also provided as debugging option.

DMA Controller idle status indication is separated on two information bits, reflecting the internal structure: DMAC AIF IDLE (Application Interface Controller) and DMAC DQH IDLE (Descriptor Queue Handler).

The Application Interface Controller, which is connected to a specific CSPT Unit, signals idle when it is willing / ready to process DMA transmit data.

The Descriptor Queue Controller signals idle when it is not performing any descriptor load or update operation.

Consequently, if both idle states are concurrently asserted, the DMA Controller is in idle.

### 5.2.3 ADC Data Acquisition

Data acquisition is performed via four separate CSPT (Capture, Storage, Processing and Transmission) Units (A/B/C/D). These units are configured via independent configuration register sets.

Although a different configuration is possible for the CSPT Units, settings shall be the same for all units.

Every unit is linked to a specific physical ADC and a specific DMA Controller. The mapping is as follows:

- Unit A: ADC Channel #07 #00, DMA Controller #0

- Unit B: ADC Channel #15 #08, DMA Controller #1

- Unit C: ADC Channel #23 #16, DMA Controller #2

- Unit D: ADC Channel #31 #24, DMA Controller #3

CSPT Units are functional identical, meaning that the subsequent description is common for all.

The functional configuration of a unit is performed via a set of three registers: CSPT Control Register and CSPT Data Register #0 (Pre-Trigger Sample Count) and #1 (Post-Trigger Sample Count).

Note that the CSPT configuration should be defined (via writes into the defined registers) before any unit is enabled. In accordance with that, before changing the configuration, all units have to be disabled.

The CSPT unit applies a static data source mode (CSPT DSM) and data acquisition mode (CSPT DAM).

The data source mode defines that ADC data is stored within the on-board DDR3 memory (data sink). The memory content is in-turn used as source for DMA host transfers (data source). Consequently, the DDR3 memory is used as ADC data buffer.

The CSPT unit operates due to performance considerations on different memory (mapping afterwards).

- Unit A: ADC Channel #07 #00, DDR3 Memory #0

- Unit B: ADC Channel #15 #08, DDR3 Memory #0

- Unit C: ADC Channel #23 #16, DDR3 Memory #1

- Unit D: ADC Channel #31 #24, DDR3 Memory #1

The data acquisition mode allows selecting an amount of pre-trigger data stored and / or post-trigger data to be stored within the on-board DDR3 memory. Based on this technique, standard pre- and post-trigger as well as around-trigger data acquisition can be performed.

The Pre-Trigger Sample Count (CSPT\_PRT\_SC), resident within CSPT Data Register #0, defines the number of sample to be captured before the trigger. Whereas the Post-Trigger Sample Count (CSPT\_POT\_SC), resident within the CSPT Data Register #1, defines the number of sample to be captured after the trigger.

The sum of both values must not exceed the total memory depth to avoid data overwriting (refer table below).

| Memory Depth             | Maximum Sample Count per<br>Channel |

|--------------------------|-------------------------------------|

| 2x 256Mbyte (default)    | 8M                                  |

| 2x 512Mbyte (optionally) | 16M                                 |

| 2x 1GByte (optionally)   | 32M                                 |

Table 5-1: Maximum Sample Count per Channel

For pre-trigger data acquisition, the CSPT units start writing ADC channel data into the DDR3 memory after they are enabled. The memory is used as cyclic / ring buffer, oldest samples are replaced by current ones.

Caused by trigger input detection, either post-trigger data acquisition continues if data should be captured (CSPT\_POT\_SC not equal to 0x00000000) or the DMA data transfer comes next.

During post-trigger data acquisition, the CSPT units write ADC channel data into the DDR3 memory. Writing is performed until the defined sample count (CSPT\_POT\_SC) has been stored. Overwriting pre-trigger with post-trigger data is inhibited and results in an error reporting (CSPT\_ERR, Application Status Register). Data is still valid in such cases and used for subsequent DMA data transfer.

Following the data acquisition phase, the DMA data transfer is performed, using the memory-stored data.

Under normal operation, the CSPT Units terminate the DMA Buffer that is currently used by the associate DMA Controller after the desired number of samples (sum of pre- and post-trigger sample count) has been transferred to the DMA Controller Buffer.

Caused by the automatic DMA Buffer termination (CSPT\_ABT), all pending data is flushed from the DMA Controller Buffer and the current active DMA Buffer (Descriptor) is terminated, including signaling the selected interrupts.

In case that a Pseudo-Streaming Operation is desired, the CSPT Automatic Buffer Termination can be disabled. In consequence, a DMA Buffer (Descriptor) is only terminated if its memory space is exhausted. This allows filling a DMA/Host Memory Buffer with multiple CSPT acquisition cycles.

In this operation mode, buffer termination can be manually initiated by the CSPT Unit Software Buffer Termination command (CSPT SW BTERM).

The functional configuration registers are surrounded by a set of three application registers: Application Control Register, Application Command Register and Application Status Register.

These registers group (combine) additional CSPT control information and allow a concurrent appliance to the different CSPT units.

In order to simplify the data processing, the physical ADC input data is, irrespective of the adjusted incoming bit width (12 or 14 bit) extended to 16 bit (internal data processing vector width per channel).

This width extension applies a most-significant bit mapping technique, causing lower data bits to be zero. In accordance with that, the highest (left-most) ADC data bit is located at the highest (left-most) position. Lower ADC data bits follow in a descending order.

| Internal Data<br>Processing<br>Vector (16 Bit) | 12 Bit (-10R) | 14 Bit (-11R) |

|------------------------------------------------|---------------|---------------|

| 15                                             | 11            | 13            |

| 14                                             | 10            | 12            |

|                                                |               |               |

| 6                                              | 2             | 4             |

| 5                                              | 1             | 3             |

| 4                                              | 0             | 2             |

| 3                                              |               | 1             |

| 2                                              | Zero          | 0             |

| 1                                              | 2610          | Zoro          |

| 0                                              |               | Zero          |

Table 5-2: ADC data alignment

The internal data processing vector width per channel is used for the Register Interface ADC Channel [xx] Data Register und the DMA data transfer via CSPT Units.

Data acquisition is initiated by stimulating the selected external trigger input (CSPT External Trigger) or via the software trigger input (CSPT Unit Software Trigger Input). The external input can be disabled while the software input is always available.

Note that the external trigger input is subdued an edge evaluation and level mode is not supported.

#### 5.2.4 I2C Bridge

The I2C Bridge provides a simplified interface that allows performing standard byte reads and writes but also advanced write-read (read-after-write) transfers.

The bridge is based on an I2C master for the actual, physical I2C bus access, which in-turn is encapsulated by a register interface wrapper, providing the following function description.

Note that the I2C master is not multi-master capable.

As long as the I2C master is not enabled (I2C\_MST\_EN), its logic is held in reset state (register map values show default values) and all initiated operation are ignored.

During functional operation, different operations can be performed on a target I2C bus: Standard Write, Standard Read and Write-Read. Standard Write and Read are variations of the Write-Read Command.

The I2C Bridge Command Register contains corresponding self-clearing commands, to initiate I2C operations.

A bus operation can be initiated only if the I2C master is in its idle state (MST\_IDLE). Operations initiated during its busy state are lost and will not been captured or queued for later processing.

The I2C Bridge Status Register provides information about the current functional state of an I2C master.

#### **Write-Read Operation**

A Write-Read is initiated via command WRS OP CMD within I2C Bridge Command Register.

This advanced I2C bus access technique allows writing a number of bytes (WRS\_SWR\_DCNT) followed by reading of a defined number of bytes (WRS\_SRD\_DCNT). So it is possible to combine a proceeding write and a subsequent read operation.

In case that any of this byte numbers is zero, the corresponding operation is not performed. Hence, the Write-Read operation behaves like a Standard Write if WRS\_SRD\_DCNT is 0x00 respectively behaves like a Standard Read if WRS\_SWR\_DCNT is 0x00.

Due to a Write-Read Command an I2C target access will be initiated if the I2C master is in idle state.

Irrespective of whether a write will be executed or only a read, an I2C STA (start-sequence) is generated to claim the bus. In case that both, a write and a read are executed, another STA (re-start) is generated between the two operations.

Following the STA sequence, the I2C slave is addressed, using the bus (I2C\_BUS\_NUM) and address information (I2C\_DEV\_NUM) provided within the I2C Bridge Command Register.

The successful addressing of the selected I2C slave is reported via DEV\_DET inside the I2C Bridge Status Register. This information remains stable until the next I2C operation is initiated. The fault that the selected slave cannot be addressed causes the master to return to its idle state with the information is not set.

After successful addressing, the selected number of bytes to write is transferred if the corresponding number (WRS\_SRD\_DCNT) is not 0x00. It is expected that the slave acknowledges every write cycle (ACK). If the slave signals a not acknowledge (NACK), the I2C operation is aborted and an error is reported (DEV\_OP\_ERR).

Write data is read from the I2C Write Data FIFO. The I2C Bridge Status Register provides information about how many bytes are available for writing (WR DFIFO CFL).

If there are no bytes to read (WRS\_SRD\_DCNT is 0x0), processing ends. Otherwise a restart sequence with another addressing phase follows (same procedure as preceding the write operation).

Afterwards the selected number of bytes to read is requested (transferred) from the selected I2C slave.

Read data is stored within the I2C Read Data FIFO. Register I2C Bridge Status Register provides information about how many bytes are available for reading (RD\_DFIFO\_CFL). The master acknowledges every read (ACK), except the last one (NACK), to correctly terminate the read operation.

Every access will end by generating an I2C STO (stop-sequence) to release the bus.

Write and read data are provided respective obtained via 32 bit registers. Write data transmission selects the least significant register byte first, upper bytes follow in an ascending order. The same order is applied by storing read data.

For interrupt controlled processing the Module Interrupt Status Register is capable of signaling the end of an initiated I2C bus operation (I2C\_BRDG\_CP). Interrupt signalisation can be controlled through the Module Interrupt Enable Register (I2C\_BRDG\_CP EN).

An interrupt is generated after an initiated operation is terminated and before the I2C master enters its idle state (MST\_IDLE). In accordance to that, the fault of a loss of arbitration (BUS\_ARBL) and/or erroneous operation (DEV\_OP\_ERR), will also result in an interrupt generation.

# **5.3 Board Configuration Controller (BCC)**

The TAMC532 provides a board configuration controller (BCC) to support the following tasks:

- Power sequencing

- Level shifting for various signals

- Power-up configuration of on-board clocking resources

- Power-up configuration and direction control of on-board M-LVDS transceivers

- Power-up configuration of on-board ADCs

After power-up, the FPGA can gain access to the configuration interfaces of all on-board devices. Two I2C interfaces between FPGA and BCC (BCC-I2C and Configuration-I2C) are used for this purpose. If necessary, the BCC bridges the I2C traffic from the FPGA to the different device specific interfaces. On-board devices with I2C interfaces are directly accessible by the FPGA via Configuration I2C.

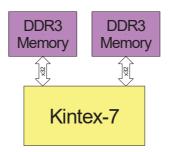

# 5.4 DDR3 Memory

Two Banks of DDR3 Memory with 32 Bit data bus each provide a total of 512Mbyte. This is sufficient for storing a total of 256Msamples, or 8Msamples from each ADC channel. At 10MHz sample frequency, the memory allows to make 800ms snapshots of all ADCs.

Figure 5-2: DDR3 Memory Interfaces

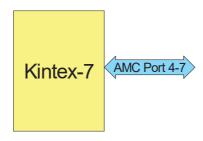

### 5.5 Fabric Interfaces

The TAMC532 provides the following fabric interfaces:

• x4 Multi-Gigabit Link between FPGA and AMC Fat Pipe Region (e.g. AMC port 4-7)

Figure 5-3: Fabric Interfaces

### 5.5.1 PCI-Express

AMC Port 4-7 is directly connected to the FPGAs Multi-Gigabit Transceivers. This allows connecting the TAMC532 to a PCI-Express environment.

## 5.6 Flash Memory

The TAMC532 provides SPI flash devices that are used to store the FPGA firmware. After power-up, the FPGA automatically loads its firmware.

# 5.7 ADC Clocking

From a top level view, the ADC clocking structure of the TAMC532 provides 4 clock inputs and 9 clock outputs.

Figure 5-4: ADC Clocking Overview

Clock sources are TCLKA and TCLKB from the AMC connector, RTM\_CLK0 from Zone 3 Connector or the on-board generated LOCAL ADC CLK.

LOCAL\_ADC\_CLK is generated by a programmable clock source and 50MHz by default. It is possible to modify the frequency of this clock if necessary.

By default, all ADCs get the same phase aligned clock. If the input clock frequency is less than the minimum ADC input clock frequency (10MHz), the Clocking structure is able to up-scale the input frequency.

To compensate routing delays or to phase align several TAMC532, individual phase-shift and delay elements can be used for each of the ADC clocks.

Initial setup of the ADC Clocking Structure is done by the BCC. The FPGA can modify this setup by writing to the corresponding BCC registers via BCC\_I2C.

The following figure shows a detailed view of the ADC Clocking Structure. The blue arrows indicate the control interfaces that are connected to the BCC.

Figure 5-5: ADC Clock Generation and Distribution Structure

### 5.7.1 Crosspoint Switch

The Crosspoint switch allows routing any signal from its 4 inputs to any of its 4 outputs. Configuration of the crosspoint switch is done via BCC.

#### 5.7.2 LMK04806

The minimum Sampling Frequency of the ADCs is 10MHz. To support slower external clock sources, the LMK04816 can multiply the external clock to a frequency >10MHz using its dual PLL structure.

In addition, this dual PLL structure allows zero-delay operation with internal loopback. Zero-delay operation is important to guarantee a fixed phase relationship between the slow input frequency and the multiplied (fast) output frequency for the ADCs.

Due to the nature of the dual PLL structure, the input frequency has a low limit of 10kHz. To support any input frequency above 10kHz, the first PLL makes use of an in-system programmable VCXO. See chapter "Mandatory Devices" for the exact device type.

Using the PLLs is also necessary to make the full phase-shift capabilities of the LMK04816 working, which allow shifting the output clocks in up to 522 steps of half PLL-frequency. Each output can be shifted individually.

Bypassing the PLLs is also possible. In this mode, the clock at CLKin1 can be used to clock the ADCs directly.

An analog delay of up to 575ps (25ps step) is available for each output group, independent from the operational mode of the LMK04806.

#### 5.7.3 VCXO

The VCXO frequency has to be an integer multiple of the input frequency.

#### 5.7.4 ADCs

The ADCs itself have the capability to internally use a divided version of their input clock. By default this feature is disabled. The ADCs are directly using their input clocks.

#### 5.7.5 TCLKB

By default, the output buffer of TCLKB is disabled. The User can enable the buffer by writing to the corresponding BCC register via BCC\_I2C.

### 5.7.6 AMC\_TCLK

Any of the four crosspoint switch inputs can be connected to AMC\_TCLK. By default, the output buffer of AMC\_TCLK is disabled. Only if ZONE3\_EN is high, the User FPGA can enable the buffer by writing to the corresponding BCC register via BCC\_I2C. If ZONE3\_EN is going low the buffer is immediately disabled.

### 5.7.7 AMC\_CLK0

Any of the four crosspoint switch inputs can be connected to AMC\_CLK0. By default, the output buffer of AMC\_CLK0 is disabled. Only if ZONE3\_EN is high, the User can enable the buffer by setting the DIP Switch accordingly. If ZONE3\_EN is going low the buffer is immediately disabled.

## 5.8 Trigger and GPIO

The TAMC532 provides access to several GPIO signals at the AMC Connector and the Zone 3 Interface. Each of these signals can be used as a trigger input.

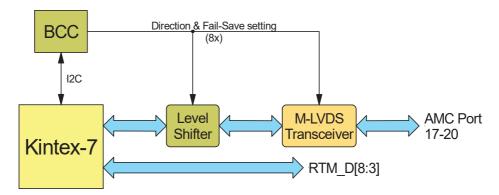

Figure 5-6: M-LVDS I/O

AMC Port 17-20 Rx and Tx Differential Pairs are all routed to eight M-LVDS Transceivers that convert the differential signals to single ended signals. At power-up, the transceivers are all configured as inputs, "reading" the signal from the AMC backplane. If desired, each Transceiver can individually be reconfigured as output by the user. To save FPGA pins, the Output-enable signals of the M-LVDS transceivers are not directly connected to the FPGA. Instead, they are connected to the Board-Configuration-Controller (BCC), which is connected to the FPGA via an I2C interface.

Zone 3 signals D[8:3]± are directly connected to FPGA pins.

D[8:5]± are used as RTM Trigger Inputs [0:3]. The IO-Standard is LVDS.

D[4]± is not used, but connected to FPGA pins with 2.5V IO-voltage.

D[3]+ is used as SCL of the RTM I2C-Bus, 2.5V IO-voltage.

D[3]- is used as SDA of the RTM I2C-Bus, 2.5V IO-voltage.

# 5.9 Analog Inputs

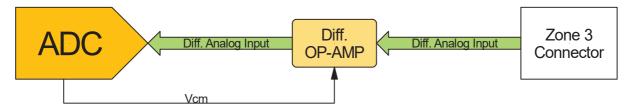

The TAMC532 provides 32 differential analog inputs. An operational amplifier with unity gain is used for each analog input to shift the analog input signal to the common-mode voltage of the ADC.

Figure 5-7: Single Analog Input

Four Octal ADCs are used on the TAMC532, each combining eight ADCs into a single chip. As a result, only one data clock and one frame clock signal is needed to sample the serial data streams of 8 ADCs into the FPGA. As a side effect, all eight ADCs of a group use the same sample clock.

ADC Data is output as one serial double data rate stream per ADC. The resulting data rate is the product of sample rate and ADC resolution. Data format used is 2's Complement, MSB first.

Figure 5-8: 8 x Analog Input Group

To save power, all operational amplifiers are powered down when the ZONE3\_EN signal is low. This includes the case that no or an incompatible µRTM is connected to the TAMC532.

### 5.9.1 ADC Sample Clock

The sample clock provided to the ADCs (ADC\_CLK) has to be in the range of 10MHz to 50MHz. Depending on ADC resolution and FPGA Speed grade, sample frequencies above 50 MHz may be possible.

In each case, the ADCs have to be reset to guarantee proper operation after a clock change. It will take about 3\*10^6 sample clock cycles to complete this reset. During reset, the ADCs deliver no or random data.

Changing the Frequency Set via the BCC (Frequency Adjustment Control Register) automatically reinitializes the ADCs, including the ADC reset.

### 5.9.2 Input Voltage Range

Each input is capable to digitize differential analog voltages of up to  $\pm 1V$  at a common mode voltage of 0V. I.e. that each of the two traces that build the differential pair is allowed to swing between the absolute voltages -0.5V and +0.5V measured against ground.

### 5.10 Debug

#### 5.10.1 LEDs

4 LEDs are provided by the TAMC532, which are directly controlled by the FPGA. Additional LEDS display basic board Status Information.

For more information about the front-panel LEDs, please refer to chapter "LED Indicators".

#### 5.10.2 UART

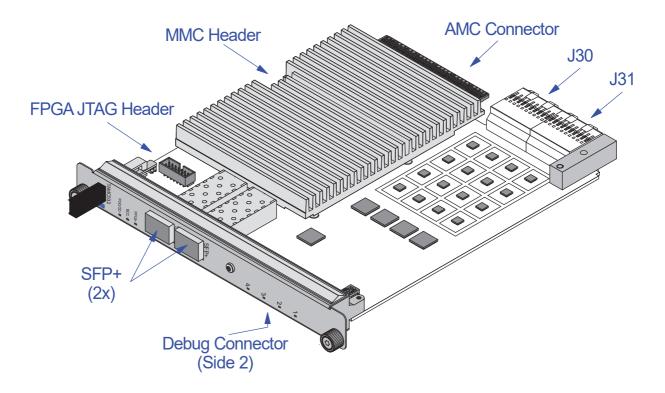

The TAMC532 provides a UART on the Debug Connector. The UART is used by the MMC and provides IPMI related debug information at 38400 baud.

#### 5.10.3 JTAG

The TAMC532 provides 4 different ways to gain access over the JTAG-Chain the Kintex-7 is part of. It can be accessed by:

- (1) The Module Management Controller (MMC)

- (2) the FPGA JTAG connector

- (3) the Debug Connector

- (4) the AMC connectors JTAG interface

When connecting a cable to one of the interfaces the chain is automatically connected to it. If multiple cables are connected, the cable with the highest priority is selected. E.g. the AMC Connectors JTAG Interface is only usable when no other cables are connected.

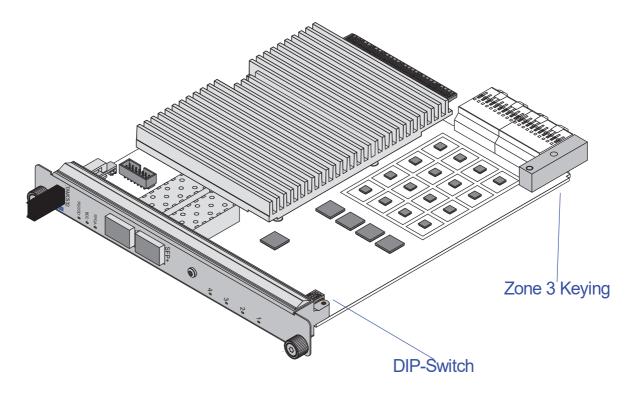

If a  $\mu$ RTM is connected via the Zone 3 connectors, also the  $\mu$ RTM JTAG devices are included into the JTAG chain. The DIP Switch can be used to exclude the  $\mu$ RTM from the AMCs JTAG chain.

### 5.11 Reset

A Reset signal is provided to the FPGA for 200ms after successful FPGA configuration.

### 5.12 µRTM Detection

If a compatible  $\mu$ RTM is detected, ZONE3\_EN is set high to signal the existence of a compatible  $\mu$ RTM to the FPGA, and all Zone 3 Interfaces are enabled. When ZONE3\_EN is going low, the FPGA disables all its Zone 3 interfaces.

# 6 Addressable Resources

This chapter describes system resources, such as memory mapping, register set and default interrupt request assignments.

### 6.1 FPGA

#### 6.1.1 Structural Description

The firmware is separated into two main parts: the PCIe Framework Unit and the Application Logic Unit.

The PCIe Framework Unit provides an application logic front-end module. Components necessary to handle PCI Express traffic, the software registers, the bridge functionality and the ADC interfaces resident within this part. For ADC data transfer via DMA from the module into the host memory, the framework contains also four independent software-configurable scatter-gather DMA controllers.

The Application Logic Unit contains four components for capturing, storing, processing and transmitting (CSPT) ADC channel data. There is one component for one physical ADC. The components use on-board DDR3 memory for storing the data locally.

The PCIe accessible software register set provides fundamental control of the firmware function logic.

A register subset is used within the framework for reading module status information and controlling base functions. Another register subset is mapped into the application function unit.

Three separate bridge interfaces are included to allow accessing the different I2C busses on the TAMC532 (BCC, Payload and RTM). Every bridge interface owns an independent register set to stimulate the connect I2C master.

In addition, another bridge allows accessing the connected SPI flash device (optional feature). It is linked like the I2C masters above.

The below figure depicts this SOC structure on a component-based level.

Figure 6-1: TAMC532 Firmware SOC Structure

# **6.1.2 PCIe Configuration**

| PCI CFG<br>Register | Write '0' to a                           |          | PCI<br>writeable | Initial Values<br>(Hex Values) |                    |           |             |

|---------------------|------------------------------------------|----------|------------------|--------------------------------|--------------------|-----------|-------------|

| Address             | 31 24                                    | 23       | 16               | 15 8                           | 7 0                |           |             |

| 0x00                | De                                       | ice ID   |                  | Vend                           | lor ID             | N         | 8214 1498   |

| 0x04                | S                                        | tatus    |                  | Com                            | mand               | Υ         | 0480 000B   |

| 0x08                |                                          | Clas     | s Code           |                                | Revision ID        | N         | 068000 01   |

| 0x0C                | BIST                                     | Head     | er Type          | PCI Latency<br>Timer           | Cache Line<br>Size | Y[7:0]    | 00 00 00 08 |

| 0x10                | PCI B                                    | ase Add  | ress 0 for       | Local Address S                | Space 0            | Υ         | FFFFF000    |

| 0x14                | PCI B                                    | ase Add  | Space 1          | N                              | 00000000           |           |             |

| 0x18                | PCI B                                    | ase Add  | Space 2          | N                              | 00000000           |           |             |

| 0x1C                | PCI B                                    | ase Add  | N                | 00000000                       |                    |           |             |

| 0x20                | PCI B                                    | ase Add  | ress 4 for       | Local Address S                | Space 4            | N         | 00000000    |