NAMC-ARRIA10-FMC AMC-FMC Carrier Module Technical Reference Manual V1.4 HW Revision 1.5

Ehlbeek 15a 30938 Burgwedel fon 05139-9980-0 fax 05139-9980-49

www.powerbridge.de info@powerbridge.de

The NAMC-ARRIA10-FMC has been designed by:

N.A.T. GmbH Konrad-Zuse-Platz 9 53227 Bonn-Oberkassel

Phone: +49 / 228 / 965 864 - 0 Fax: +49 / 228 / 965 864 - 10

Internet: http://www.nateurope.com

### Disclaimer

The following documentation, compiled by N.A.T. GmbH (henceforth called N.A.T.), represents the current status of the product's development. The documentation is updated on a regular basis. Any changes which might ensue, including those necessitated by updated specifications, are considered in the latest version of this documentation. N.A.T. is under no obligation to notify any person, organization, or institution of such changes or to make these changes public in any other way.

We must caution you, that this publication could include technical inaccuracies or typographical errors.

N.A.T. offers no warranty, either expressed or implied, for the contents of this documentation or for the product described therein, including but not limited to the warranties of merchantability or the fitness of the product for any specific purpose.

In no event will N.A.T. be liable for any loss of data or for errors in data utilization or processing resulting from the use of this product or the documentation. In particular, N.A.T. will not be responsible for any direct or indirect damages (including lost profits, lost savings, delays or interruptions in the flow of business activities, including but not limited to, special, incidental, consequential, or other similar damages) arising out of the use of or inability to use this product or the associated documentation, even if N.A.T. or any authorized N.A.T. representative has been advised of the possibility of such damages.

The use of registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations (patent laws, trade mark laws, etc.) and therefore free for general use. In no case does N.A.T. guarantee that the information given in this documentation is free of such third-party rights.

Neither this documentation nor any part thereof may be copied, translated, or reduced to any electronic medium or machine form without the prior written consent from N.A.T. GmbH.

This product (and the associated documentation) is governed by the N.A.T. General Conditions and Terms of Delivery and Payment.

#### Note:

The release of the Hardware Manual is related to a certain HW board revision given in the document title. For HW revisions earlier than the one given in the document title please contact N.A.T. for the corresponding older Hardware Manual release.

## **Table of Contents**

| TABLE O                                                                               | F CONTENTS                                                                                                                                              |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF                                                                               | TABLES5                                                                                                                                                 |

| LIST OF                                                                               | FIGURES                                                                                                                                                 |

| CONVEN                                                                                | TIONS                                                                                                                                                   |

| <b>1 INT</b>                                                                          | RODUCTION                                                                                                                                               |

| 2 OVE                                                                                 | RVIEW                                                                                                                                                   |

| 2.1<br>2.2                                                                            | Major Features                                                                                                                                          |

| 3 BOA                                                                                 | RD INSPECTION                                                                                                                                           |

| 3.1<br>3.2<br>3.3<br>3.4                                                              | LOCATION DIAGRAM                                                                                                                                        |

| 4 FPG                                                                                 | A OPERATION                                                                                                                                             |

| 4.2<br>4.2.2<br>4.2.2<br>4.3<br>4.3<br>4.3.2<br>4.3.2<br>4.3.2<br>4.3.4<br>4.4<br>4.5 | 2Embedded USB Blaster II183JTAG Multiplexer Logic19CONFIGURATION & BOOTING201HPS boot sources202FPGA boot sources203HPS Dedicated I/O-Pin-Assignments22 |

|                                                                                       | CK DISTRIBUTION SYSTEM                                                                                                                                  |

|                                                                                       | OPERATION                                                                                                                                               |

| _                                                                                     | SUPPORTED FMC'S                                                                                                                                         |

| 8 TRO                                                                                 | UBLESHOOTING                                                                                                                                            |

| 9 KNC                                                                                 | OWN LIMITATIONS                                                                                                                                         |

|                                                                                       | MC-CONNECTOR I/O-PIN-MAP43                                                                                                                              |

| 11 BO                                                                                 | OARD SPECIFICATION                                                                                                                                      |

|                                                                                       | STALLATION                                                                                                                                              |

|                                                                                       | NOWN BUGS / RESTRICTIONS                                                                                                                                |

| APPEND                                                                                | IX A: REFERENCE DOCUMENTATION60                                                                                                                         |

| APPEND                                                                                | IX B: DOCUMENT'S HISTORY                                                                                                                                |

## **List of Tables**

| Table 1: List of used abbreviations                               | 6  |

|-------------------------------------------------------------------|----|

| Table 2: SW2 DIP switch configuration                             | 12 |

| Table 3: SW3 DIP switch configuration                             | 13 |

| Table 4: SW3 DIP switch configuration (only revision 1.0 and 1.1) | 13 |

| Table 5: LED functions                                            | 15 |

| Table 6: JTAG Connector Signal Mapping                            | 18 |

| Table 7: HPS dedicated I/O Pin Assignments                        | 22 |

| Table 8: HPS/FPGA shared I/O Pin Assignments Part 1               | 23 |

| Table 9: HPS/FPGA shared I/O Pin Assignments Part 2               | 32 |

| Table 10: PLL Clocks                                              | 37 |

| Table 11: Board Specification                                     | 54 |

## **List of Figures**

| Figure 1: Board View                               | 8  |

|----------------------------------------------------|----|

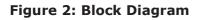

| Figure 2: Block Diagram                            | 10 |

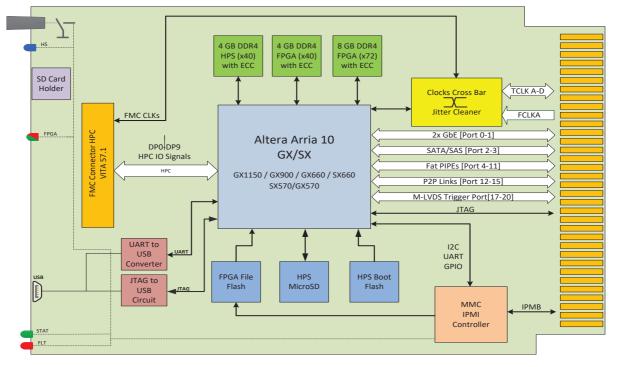

| Figure 3: Board View (TOP)                         | 11 |

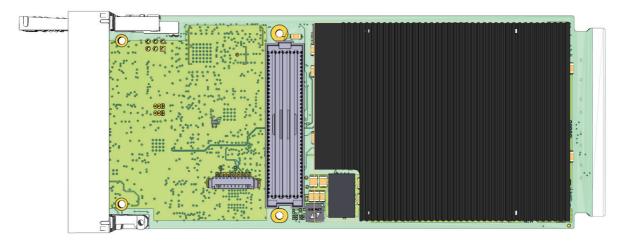

| Figure 4: Board View (BOT)                         | 11 |

| Figure 5: DIP Switch locations                     | 12 |

| Figure 6: FMC Baseboard Connector                  | 14 |

| Figure 7: FMC to FPGA Signalling                   | 14 |

| Figure 8: Front Panel                              | 15 |

| Figure 9: FPGA Resource Overview                   | 16 |

| Figure 10: External JTAG Header                    | 17 |

| Figure 11: Intel Programming Cable II              | 18 |

| Figure 12: JTAG switching logic                    | 19 |

| Figure 13: Create Indirect JTAG configuration File | 21 |

| Figure 14: Program FLASH memory                    |    |

| Figure 15: Serial Console COM Port Settings        | 34 |

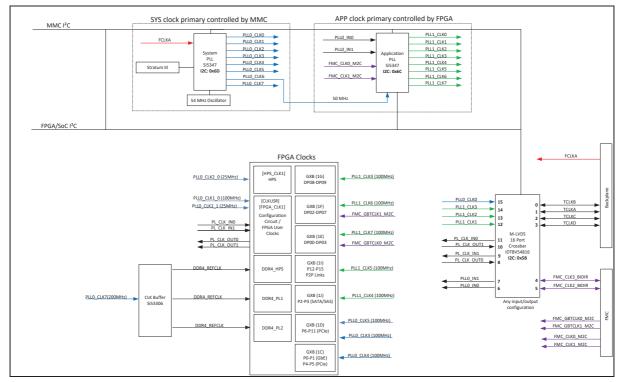

| Figure 16: Clock Distribution System               |    |

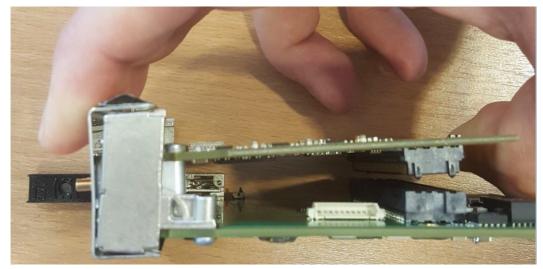

| Figure 17: Installing FMC Module Part 1            | 39 |

| Figure 18: Installing FMC Module Part 2            | 40 |

| Figure 19: FMC Connector IO Assignments            | 43 |

### Conventions

If not otherwise specified, addresses and memory maps are written in hexadecimal notation, identified by 0x. The following table gives a list of the abbreviations used in this document.

| Abbreviation     | Description                                     |  |  |

|------------------|-------------------------------------------------|--|--|

| AMC              | Advanced Mezzanine Card                         |  |  |

| AS               | Active Serial                                   |  |  |

| СОМ              | Communication Port                              |  |  |

| CPU              | Central Processing Unit                         |  |  |

| CvP              | Configuration via Protocol                      |  |  |

| DBG              | Debug                                           |  |  |

| DDR SDRAM        | Double Data Rate Synchronous Dynamic RAM        |  |  |

| DIP SW           | Dual In-Line Switch                             |  |  |

| EEPROM           | Electrically Erasable PROM                      |  |  |

| ECC              | Error Correcting Code                           |  |  |

| FCLK             | Fabric Clock                                    |  |  |

| FMC              | FPGA Mezzanine Card                             |  |  |

| FPGA             | Field Programmable Gate Array                   |  |  |

| FRU              | Field Replaceable Unit                          |  |  |

| GbE              | Gigabit Ethernet                                |  |  |

| GND              | Ground                                          |  |  |

| HPC              | High Pinout Connector                           |  |  |

| HPS              | Hard Processor System                           |  |  |

| PS               | Hot Swap                                        |  |  |

| I <sup>2</sup> C | Inter-Integrated Circuit                        |  |  |

| I/O              | Input / Output                                  |  |  |

| IP               | Internet Protocol                               |  |  |

| IPMI             | Intelligent Platform Management Interface       |  |  |

| JSM              | JTAG Switch Module                              |  |  |

| JTAG             | Joint Test Action Group                         |  |  |

| LED              | Light Emitting Diode                            |  |  |

| LPC              | Low Pinout Connector                            |  |  |

| μC               | Microcontroller                                 |  |  |

| μΤϹΑ             | Micro Telecommunications Computing Architecture |  |  |

| ММС              | Module Management Controller                    |  |  |

| (M)LVDS          | Multipoint Low Voltage Differential Signalling  |  |  |

| P2P              | Peer-To-Peer                                    |  |  |

| PCB              | Printed Circuit Board                           |  |  |

| PCI(e)           | Peripheral Component Interconnect (Express)     |  |  |

| PS               | Passive Serial                                  |  |  |

| PS               | Processing System                               |  |  |

| QSPI             | Quad SPI                                        |  |  |

| RAM              | Random Access Memory                            |  |  |

| RF               | Radio Frequency                                 |  |  |

| RGMII            | Reduced Gigabit Media Independent Interface     |  |  |

### Table 1: List of used abbreviations

| Abbreviation | Description                                 |  |  |  |

|--------------|---------------------------------------------|--|--|--|

| (P)ROM       | (Programmable) Read Only Memory             |  |  |  |

| PLL          | Phase Locked Loop                           |  |  |  |

| SAS          | Serial Attached SCSI                        |  |  |  |

| SATA         | Serial Advanced Technology Attachment       |  |  |  |

| SCSI         | Small Computer System Interface             |  |  |  |

| SD-Card      | Secure Digital Memory Card                  |  |  |  |

| SerDes       | Serializer / Deserializer                   |  |  |  |

| SGMII        | Serial Gigabit Media Independent Interface  |  |  |  |

| SoC          | System On A Chip                            |  |  |  |

| SRIO         | Serial Rapid I/O                            |  |  |  |

| TCKL         | Telecom Clock                               |  |  |  |

| UART         | Universal Asynchronous Receiver/Transmitter |  |  |  |

| USB          | Universal Serial Bus                        |  |  |  |

| XAUI         | 10 GbE (via 4x 3.125 GB/s)                  |  |  |  |

# **1** Introduction

N.A.T.'s **NAMC-ARRIA10-FMC** is a high performance AMC carrier card for FMC modules. It supports HPC and LPC connector FMC modules as defined by VITA 57.1. The heart of the board is formed by the Intel/Altera Arria10 FPGA in NF40 BGA-1517 package with high count I/O to facilitate the connectivity of all required FMC HPC connector pins with the FPGA core. Intel® Arria® 10 FPGAs deliver massive performance and power consumption improvements compared to prior-generation FPGAs, both midrange and high-end devices. The board is available in various FPGA configurations beginning from SX570 over SX660 (with embedded dual ARM core CPU) up to GX1150.

The capability of carrying both HPC and LPC FMC modules allows it to be used in a wide range of applications providing data acquisition, networking, RF or other functionality. Typical applications might be wireless base stations, camera systems or generic research applications which require high speed sensor data conversions from analogue to digital.

The **NAMC-ARRIA10-FMC** is a single width AMC card available with full-size or mid-size front panels which allows it to be used in any MicroTCA chassis. The board has three FPGA/CPU dedicated high dense DDR4 memory interfaces with a total amount of up to 16 Gigabytes. To simplify the user interaction with the FPGA/SoC the front panel of the board gives access to the MircoSD card and the onboard Altera© Blaster II circuitry for comfortable JTAG access without any probe or adapter needed.

The following figure shows a photo of the **NAMC-ARRIA10-FMC.**

### Figure 1: Board View

## **2** Overview

### 2.1 Major Features

### **Form Factor**

• Single width, full-size or mid-size AMC

### **FPGA** configurations

- Intel/Altera Arria 10

- GX1150, GX900, GX660, GX570

- SX660, SX570

#### **CPU (SX variant only)**

• Dual Core ARM Cortex A9 processor, up to 1.5 GHz

#### FMC slot:

- High-Pin Count FMC slot per VITA 57.1 compliant

- Low-Pin Count FMC slot per VITA 57.1 compliant

- All HPC differential pairs (LA/HA/HB) are routed to the FPGA.

- DP0 to DP09 are routed to the FPGA

#### Memory

- Total up to 16GB of SDRAM

- 8 GB DDR4 (x72) memory bank with ECC dedicated to FPGA

- 4 GB DDR4 (x40) memory bank with ECC dedicated to FPGA

- 4 GB DDR4 (x40) memory bank with ECC dedicated to HPS or FPGA

- 128 MB HPS boot memory flash (QSPI)

- 128 MB FPGA configuration memory flash (QSPI)

- MicroSD card slot

### **Backplane Connectivity**

- Dual 1GbE connect to Port 0 and Port 1

- Ports 2 and 3 for SATA, SAS

- One x8 PCIexpress Gen3 connect to Fat-Pipe-Region Ports 4-11 or

- Dual x4 PCI express Gen3 to Fat-Pipe-Region Ports 4-7 and Ports 8-11 or

- Dual x4 SRIO Gen2 to Fat-Pipe-Region Ports 4-7 and Ports 8-11

- Any Combinations of PCIe, SRIO, XAUI (on request)

- Full AMC TCLKA-D and FCLKA connectivity (bidirectional)

- Point to point connectivity: Ports 12-15 routed to FPGA (2 x 4 LVDS)

- 8x MLVDS trigger lines (Ports 17-20)

### Front Panel

- Dual UART-USB to ARM core (SX660, SX570 only) and MMC

- AMC standard LEDs and Hot Swap Handle

- Application LEDs

### Compliance

- AMC.0 R2.0, AMC.1, AMC.2, AMC.3, AMC.4, IMPI V1.5, HPM.1

- EN60950, UL1950, RoHS

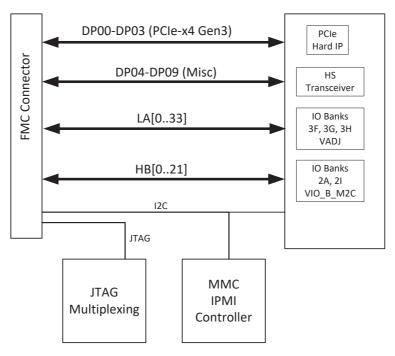

### 2.2 Block Diagram

The following figure shows a block diagram of the **NAMC-ARRIA10-FMC**.

# **3 Board Inspection**

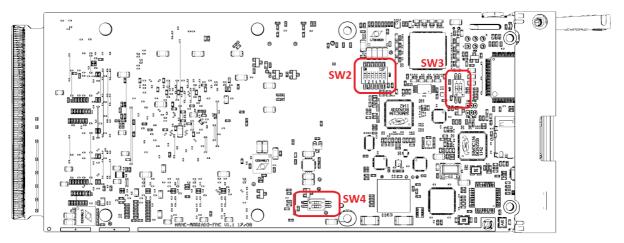

### 3.1 Location Diagram

The position of important components and connectors is shown in the following location overview. Depending on the board type it might be that the board does not include all components shown in the location diagram.

### Figure 3: Board View (TOP)

Figure 4: Board View (BOT)

## 3.2 DIP Switches

The board is configurable using DIP switches SW2, SW3 and SW4. The following figure shows the switch locations on the bottom side of the PCB.

#### Figure 5: DIP Switch locations

#### Table 2: SW2 DIP switch configuration

|          | ON                            | OFF (Factory Default)                       |

|----------|-------------------------------|---------------------------------------------|

| SW2-1    | User Logic                    | User Logic                                  |

| (Note 1) |                               |                                             |

| SW2-2    | User Logic                    | User Logic                                  |

| (Note 2) |                               |                                             |

| SW2-3    | Start FMC FRU record wizard   | Use FMC records to determine module         |

| (Note 3) | to create / edit FMC records  | requirements. If FMC records are corrupted  |

|          | during board startup (see     | or not available the carrier will not power |

|          | section 7)                    | on.                                         |

| SW2-4    | Skip parsing of FMC EEPROM    | Parsing of FMC EEPROM FRU enabled.          |

|          | FRU and power VADJ and        | VADJ, and VIO_B_M2C is set at the carrier   |

|          | VIO_B_M2C with 1.8V.          | according to the contents of the FMC        |

|          |                               | EEPROM records.                             |

| SW2-5    | Set FPGA configuration source | Set FPGA configuration source to Active     |

|          | to Passive Serial (PS)        | Serial (ASx4). It uses the EPCQ flash       |

|          |                               | device for its configuration                |

| SW2-6    | Set HPS boot source to QSPI   | Set HPS boot source to SD-Card.             |

| (Note 4) | flash memory                  |                                             |

Note 1: SW2-1 is connected to user FPGA logic (PIN\_H18)

Note 2: SW2-2 is connected to user FPGA logic (PIN\_H19)

Note 3: SW2-3 has no effect when SW2-4 is set to "ON"

Note 4: If the HPS boot source is "SD-Card" the user needs to do an Early-I/O-Release first in order for the HPS to get access to the SD card controller which is connected to FPGA logic.

See chapter 4.3 Configuration & Booting for more information.

### Table 3: SW3 DIP switch configuration

|          | ON                       | OFF (Factory Default)               |

|----------|--------------------------|-------------------------------------|

| SW3-1    | Select Backplane as JTAG | Select Embedded USB Blaster as JTAG |

|          | master                   | master                              |

| SW3-2    | Route FPGA JTAG to       | Route FMC JTAG to Backplane         |

| (Note 1) | Backplane                |                                     |

- Note 1: See section 4.2.3 for more detailed information regarding JTAG multiplexing. This dip switch is not available for PCB version greater than V1.1.

- Note 2: To use the external JTAG header as master, DIP SW3-2 needs to be turned off (Only for board revision 1.1)

- Note 3: SW3-2 has no effect on hardware revision 1.2. When selecting Embedded USB Blaster as JTAG master (SW3-1) on revision 1.2 the FMC JTAG is automatically routed to backplane.

Table 4: SW3 DIP switch configuration (only revision 1.0 and 1.1)

|       | ON                            | OFF (Factory Default)                 |

|-------|-------------------------------|---------------------------------------|

| SW4-1 | VIO_B_M2C is always           | VIO_B_M2C is switched on/off          |

|       | switched on. Voltage is equal | automatically based on FMC DC records |

|       | to VADJ (1.2 – 1.8V)          |                                       |

| SW4-2 | VREF_B_M2C is always          | VREF_B_M2C is switched on/off         |

|       | switched on. Voltage is equal | automatically based on FMC DC records |

|       | to VADJ (1.2 – 1.8V)          |                                       |

- Note: Per VITA 57.1 specification HPC FMC modules source VIO\_B\_M2C and VREF\_B\_M2C. Use this DIP switch to overwrite sourcing of these voltages regardless the FMC EEPROM contents. The FPGA cannot be used without sourcing VIOB\_M2C and VREF\_B\_M2C.

- Note: DIP switch SW4 has been replaced with MOSFET switching circuitry on hardware revision 1.2.

### 3.3 FMC Baseboard Connector

### Figure 6: FMC Baseboard Connector

The figure above shows the locations of the main FMC HPC connector (J1). Please see chapter 10 for a detailed pin map of connector J1.

The following figure shows the pin mapping between the FPGA and FMC connector.

Figure 7: FMC to FPGA Signalling

All high-speed transceiver pins are connected to FPGA transceivers. Especially DP00 to DP03 can be used with the FPGA internal PCIe-x4 hard IP controller. It is also possible to use DP00-D007 as PCIe-x8 link. All User-I/O are connected as LVDS transmission lines to the FPGA. The FPGA also has access to the FMC management bus (I<sup>2</sup>C) that can be used to read / write FMC records from within FPGA logic. The FMC JTAG signals can be routed

to the backplane using the board JTAG multiplexer logic (See Section **JTAG** for more information).

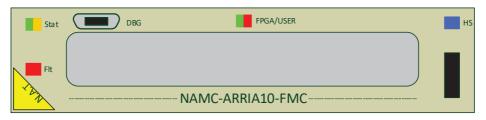

## 3.4 Front Panel & LEDs

The front panel gives access to interfaces and LEDs. The following figure shows the locations of the following utilities.

#### **Figure 8: Front Panel**

The MicroUSB Port (DBG) gives access to a dual UART interface port (MMC and FPGA) and the embedded USB blaster programmer. Both functions are merged using an USB hub.

Note: For hardware revision 1.0 and 1.1 maximum USB speed is limited to full speed (12M). USB highspeed (480M) is available from hardware revision 1.2.

| Led               | Function                                                       |                                                |                             |  |

|-------------------|----------------------------------------------------------------|------------------------------------------------|-----------------------------|--|

| FLT (Red)         | ON                                                             | Error. See error codes to figure out condition |                             |  |

|                   | OFF                                                            | Normal operation                               |                             |  |

|                   | BLINK                                                          | FMC is not cor                                 | mpatible with carrier       |  |

|                   | Error Code                                                     | Stat LED is blinking                           | FPGA is not configured      |  |

|                   |                                                                | constantly                                     |                             |  |

|                   |                                                                | Stat LED is blinking                           | Error during board          |  |

|                   |                                                                | but not constant                               | initialization. See MMC log |  |

|                   |                                                                |                                                | for more information.       |  |

| HS (Blue)         | ON                                                             |                                                | (HS Handle is pulled out)   |  |

|                   | OFF                                                            |                                                | (HS handle is pushed in)    |  |

|                   | BLINK                                                          |                                                | tion between M1 and M4      |  |

| Stat (Green)      | ON                                                             | Normal operation                               |                             |  |

|                   | OFF                                                            | During FPGA                                    | board initialization        |  |

|                   | BLINK                                                          |                                                | -                           |  |

| Stat (Yellow)     | ON                                                             | -                                              |                             |  |

|                   | OFF                                                            | Norm                                           | al operation                |  |

|                   | BLINK                                                          |                                                | not configured              |  |

| User (Green/Red)  | User LED connected to FPGA logic. When using the factory image |                                                |                             |  |

|                   | this LED toggles between GREEN/RED each second.                |                                                |                             |  |

|                   | Red: PIN_G17, High Active                                      |                                                |                             |  |

|                   | Green: PIN_F18, High Active                                    |                                                |                             |  |

| Board LED (Green) | User LED connected to HPS I/O. When using Factory Image this   |                                                |                             |  |

|                   | LED gets turned off when FPGA is configuration is done.        |                                                |                             |  |

|                   |                                                                | PIN_L18, High                                  | Active.                     |  |

#### Table 5: LED functions

## 4 FPGA Operation

### 4.1 Resource Overview

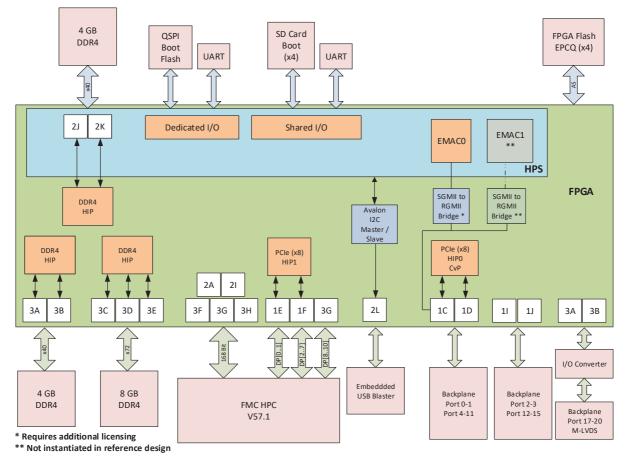

### Figure 9: FPGA Resource Overview

The figure above shows how the HPS and FPGA section within the Arria10 are connected to outside peripherals. The blue box shows all peripherals that are dedicated to the Hard Processor System in case of using the **NAMC-ARRIA10-FMC** in any SX option. The green section visualizes the fabric part of the device with internal hard or soft IPs. All orange boxes symbolize hard IPs while the soft blue boxes show soft IPs that are required for specific functions to be used. Some of the soft IPs e.g. SGMII to HPS may need additional licensing.

The Hard Processor System (HPS) has dedicated connections to a QSPI boot flash for firmware or bootloader storage, UART and 4 gigabytes of dedicated DDR4 memory. The DDR4 memory is connected to FPGA banks 2J and 2K. The SD card hard IP controller is connected to the HPS using the shared I/O section. Any function that is connected to the shared I/O will not be accessible to the HPS until the FPGA is fully configured. To speed up access to the shared IO the user can split the programming file into two parts in order to do an early I/O release from within u-boot on chip memory.

To get ethernet access from within the HPS the user will have to instantiate a SGMII to RGMII bridge that performs the conversion from 1000Base-X or SGMII backplane Ethernet to the processor's parallel internal GMII interface. This softcore contains the PCS/PMA function of the TSE (Tripple Speed Ethernet) IP Core which needs additional licensing.

The user could use the PCIE Hard IP "0" which is connected to AMC backplane port 4-11 to be used as a single x8 or x4 link. This hard IP supports Configuration via Protocol (CvP) to configure the FPGA over PCIexpress. The second PCIe Hard IP is connected to FMC high speed data lanes DP00-DP07 to create a x8 link.

In order to get I<sup>2</sup>C access to board peripherals such as the clocking multiplexer or clock generators the user has to instantiate a soft IP core (Avalon  $I^2C$ ).

To offer users a more easy and quick start with the **NAMC-ARRIA10-FMC** the board is delivered with a Quartus Prime hardware example project which implements most of the functions that are shown in Figure 9: FPGA Resource Overview. It also includes the complete FPGA pinout.

### 4.2 JTAG

### 4.2.1 External JTAG Header

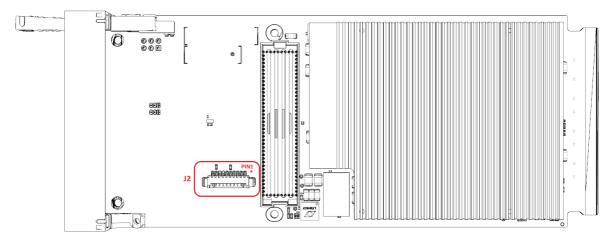

#### Figure 10: External JTAG Header

The pin out of connector J2 is shown in Figure 10: External JTAG Header. This connector gives direct access to FPGA JTAG signals. To connect to the FPGA use the JTAG connector on the top side of the carrier. Use the adapter cable that has been delivered with the board to connect the 10 pin female header of the Intel Altera USB Blaster II Programmer. **Please do only use the original programmer delivered by Altera/Intel (see figure below) in order not to damage the FPGA.**

There are several no-name low-budget copies of the blaster programming cable available that may damage the FPGA. The original programming cable can be obtained by the following part number: PL-USB2-BLASTER

| Pin | <b>Board Header Function</b> |                      | l FPGA<br>I Function (Female)         |

|-----|------------------------------|----------------------|---------------------------------------|

| 1   | ТСК                          | ТСК                  | 7 (9.4) Typ.                          |

| 2   | GND                          | GND                  |                                       |

| 3   | TDO                          | TDO                  |                                       |

| 4   | VCC (TRGT) (+1.8V)           | VCC (TRGT)           |                                       |

| 5   | TMS                          | TMS                  | 9 7 5 3 1                             |

| 6   | Processor Warm Reset         | Processor Warm Reset |                                       |

| 7   | Reserved                     | -                    | .10 (2.5)Sq. 0.15 (3.8) Typ. (.63)Sq. |

| 8   | Reserved                     | -                    | 0.70 (17.8) Typ.                      |

| 9   | TDI                          | TDI                  |                                       |

| 10  | GND                          | GND                  |                                       |

|     |                              |                      | Source: Altera UG-01150               |

Table 6: JTAG Connector Signal Mapping

- Note: Please see the official Intel/USB Download Cable II manual (UG-01150) for more detailed information.

- Note: The board uses the following male connector part: Molex 53261-1071 Suggested mating female connector cable: Molex 15134-1000

- Note: To use the external JTAG header as master, DIP SW3-2 needs to be turned off (Only board revision 1.1)

### 4.2.2 Embedded USB Blaster II

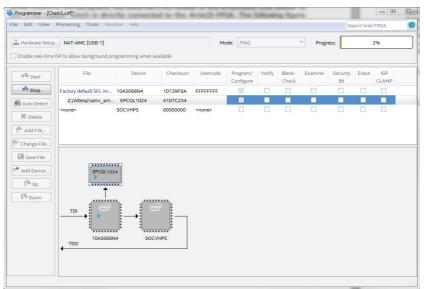

The FMC carrier board implements the USB-Blaster II circuitry on the PCB so that the user can access the FPGA using the front panel USB port. The embedded programmer will be recognized as "NAT-AMC" by the Quartus Programming Tools.

### 4.2.3 JTAG Multiplexer Logic

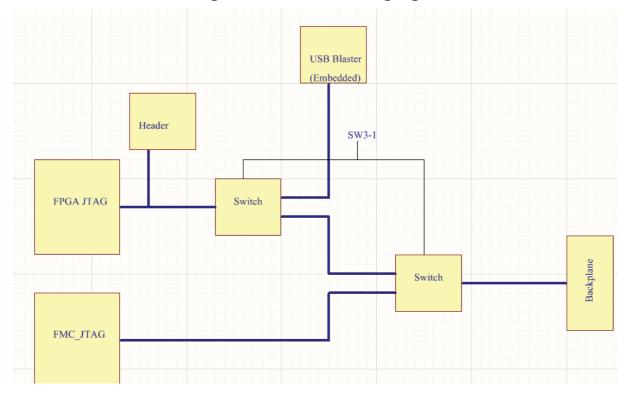

The **NAMC-ARRIA10-FMC** implements an electrical circuit to route different JTAG slaves to a specific JTAG master. Possible JTAG slaves are the Arria10 FPGA and the FMC JTAG port. The user can decide whether to route the FPGA JTAG signals or the FMC signals over the backplane to an external JTAG master (e.g. **NAT-JSM**). In case the FPGA JTAG is not routed to the backplane the external JTAG header the embedded USB-Blaster or the external JTAG header is the JTAG master which is directly connected to the Arria10 FPGA. The embedded blaster will be switched off while onboard header adapter cable is connected to the board. The following figure shows a block diagram of the JTAG switching logic which can be controlled with an onboard DIP-Switch (SW3-1).

Figure 12: JTAG switching logic

Note: On hardware revision 1.2 and newer DIP SW3-1 controls both switches simultaneously. DIP SW3-2 has no effect.

### 4.3 Configuration & Booting

### 4.3.1 HPS boot sources

Available processor boot sources on the NAMC-ARRIA10-FMC are the embedded QSPI flash memory or SD-Card. The boot source can be selected by DIP switch SW2-6 (see Table 2: SW2 DIP switch configuration). The default boot setting is to boot from QSPI memory. Depending on the peripherals being used by the HPS it is necessary for the FPGA to be fully or partially configured first. In case the HPS needs to access DRAM and shared IO connections (e.g. SD Card) it is sufficient for the FPGA at least to be configured as "Early IO Release".

#### 4.3.2 FPGA boot sources

The FPGA can be configured using Active Serial (x4) or Passive Serial programming. The boot source can be selected by DIP switch SW2-5 (see Table 2: SW2 DIP switch configuration). When using Active Serial the FPGA will load its configuration file from the EPCQ1024 on board flash memory during start up. When using Passive Serial the FPGA has to be programmed by the HPS. The default boot configuration is Active Serial (x4).

As the EPCQ1024 has no direct connection to the programming header it is necessary to do an indirect JTAG configuration through the FPGA. This can be either done by instantiating the "Intel Serial Flash Loader" IP core from the IP catalogue or by creating an indirect JTAG configuration file ".jic" with the Quartus Tool using "File  $\rightarrow$  Convert Programming Files" dialog. Referring to Figure 13: Create Indirect JTAG configuration File you will have to select the proper flash device and serial flash loader core. Click on "add Sof Page" to add the .sof File prior generated by the Quartus assembler.

#### Figure 13: Create Indirect JTAG configuration File

| ture use.<br>Conversion setup files                             |                         |                     | e the conversion setup inf                |          |                  |                                      |

|-----------------------------------------------------------------|-------------------------|---------------------|-------------------------------------------|----------|------------------|--------------------------------------|

|                                                                 | open Conversion Setup   | Data                |                                           | Save Con | version Setup    |                                      |

| Output programming                                              | file                    |                     |                                           |          |                  |                                      |

| rogramming file type                                            | e: JTAG Indirect Config | uration File (.jic) |                                           |          |                  |                                      |

| Options/Boot info                                               | Configuration device:   | EPCQL1024           | •                                         | Mode:    | Active Serial x4 |                                      |

| ile name:                                                       | output_files/bsp_flas   | h.jic               |                                           |          |                  |                                      |

| Advanced                                                        | Remote/Local update     | difference file:    | NONE                                      |          |                  |                                      |

|                                                                 |                         |                     | periph.jic and bsp_flash.co               |          |                  |                                      |

| nput files to convert                                           | Create config data      |                     |                                           |          |                  |                                      |

| nput files to convert<br>File/Data                              | Create config data      |                     |                                           |          |                  | Add Hex D                            |

|                                                                 | Create config data      | RPD (Generate bsp   | _flash_auto.rpd)                          |          |                  | Add Hex D<br>Add Sof Pa<br>Add File. |

| File/Data<br>Boot Info<br>4 Flash Loader                        | Create config data      | RPD (Generate bsp.  | _flash_auto.rpd)<br>Start Address         |          |                  | Add Sof Pa                           |

| File/Data<br>Boot Info<br>Flash Loader<br>10AS066N4             | Create config data      | RPD (Generate bsp.  | _flash_auto.rpd) Start Address 0x00000000 |          |                  | Add Sof Pa                           |

| File/Data<br>Boot Info<br>Flash Loader<br>10AS066N4<br>SOF Data | Create config data      | Properties          | _flash_auto.rpd) Start Address 0x00000000 |          |                  | Add Sof Pa<br>Add File<br>Remove     |

Once this is done you should open the Quartus Programmer from the "Tools  $\rightarrow$  Programmer" dialogue. Click on "Auto Detect" to detect the proper FPGA device. Then right click on the FPGA device and choose "Change File". Select the .jic File and enable the "Program / Configure" checkboxes.

#### Figure 14: Program FLASH memory

### 4.3.3 HPS Dedicated I/O-Pin-Assignments

The following table shows the HPS dedicated IO pin assignments. Pin functions are fixed and cannot be changed by the user.

Table 7: HPS dedicated I/O Pin Assignments

| Pin Name   | Pin Location | Function                       |

|------------|--------------|--------------------------------|

| GPIO2_IO0  | E16          | QSPI_CLK (HPS Boot Flash)      |

| GPIO2_IO1  | H16          | QSPI_IO0 (HPS Boot Flash)      |

| GPIO2_IO2  | G16          | QSPI_CSn (HPS Boot Flash)      |

| GPIO2_IO3  | H17          | QSPI_IO1 (HPS Boot Flash)      |

| GPIO2_IO4  | F15          | QSPI_IO2 (HPS Boot Flash)      |

| GPIO2_IO5  | K16          | QSPI_IO3 (HPS Boot Flash)      |

| GPIO2_IO6  | L17          | BOOTSEL1 (Controlled by MMC)   |

| GPIO2_IO7  | N19          | BOOTSEL0 (Controlled by MMC)   |

| GPIO2_IO8  | N.C.         | -                              |

| GPIO2_IO9  | N.C.         | -                              |

| GPIO2_IO10 | N.C.         | -                              |

| GPIO2_IO11 | L18          | Board LED (Green), Active High |

| GPIO2_IO12 | M17          | UART1_TX (To Front USB)        |

| GPIO2_IO13 | K17          | UART1_RX (To Front USB)        |

### 4.3.4 HPS/FPGA Shared I/O Pin Assignments

The following table shows shared pins between the HPS and FPGA. All functions are fixed and cannot be changed by the user.

| Din Namo   | Din Location | Eurotion                                          |

|------------|--------------|---------------------------------------------------|

| Pin Name   | Pin Location | Function                                          |

| GPIO0_IO0  | D18          | SD_DATA0                                          |

| GPIO0_IO1  | E18          | SD_CMD                                            |

| GPIO0_IO2  | C19          | SD_CLK                                            |

| GPIO0_IO3  | D19          | SD_DATA1                                          |

| GPIO0_IO4  | E17          | SD_DATA2                                          |

| GPIO0_IO5  | F17          | SD_DATA3                                          |

| GPIO0_IO6  | C17          | UART_TX (Shared IO Soft UART capable)             |

| GPIO0_IO7  | C18          | UART_RX (Shared IO Soft UART capable)             |

| GPIO0_IO8  | N.C.         | -                                                 |

| GPIO0_IO9  | N.C.         | -                                                 |

| GPIO0_IO10 | N.C.         | -                                                 |

| GPIO0_IO11 | N.C.         | -                                                 |

| GPIO0_IO12 | H18          | Input from DIP SW2-1                              |

| GPIO0_IO13 | H19          | Input from DIP SW2-2                              |

| GPIO0_IO14 | F18          | FPGA_LED1 (Green, Front Panel)                    |

| GPIO0_IO15 | G17          | FPGA_LED0 (Red, Front Panel)                      |

| GPIO0_IO16 | E20          | RESERVED                                          |

| GPIO0_IO17 | F20          | RESERVED                                          |

| GPIO0_IO18 | G20          | Positive Clock Output (PL_CLK_OUT0_P) from        |

|            |              | Clock Switch. See Section                         |

|            |              | Board Support Package                             |

|            |              | The board support package is a combination of     |

|            |              | hardware and software logic which is generated    |

|            |              | by Intel Design Sofware Quartus Prime Pro 17.0    |

|            |              | This tool can be download at the IntelFPGA        |

|            |              | Download Center. The BSP is production            |

|            |              | programmed and delivered with the NAMC-           |

|            |              | ARRIA10-FMC hardware board.                       |

|            |              |                                                   |

|            |              | The board support package contains the            |

|            |              | following items:                                  |

|            |              | Quartus 17.0 Example Project, Block               |

|            |              | Design Level, QSYS                                |

|            |              | Linux Distribution on SD Card                     |

|            |              | Instructions how to generate & compile            |

|            |              | everything (Yocto 2.4.2)                          |

|            |              | The exampled Question 17.0 km l                   |

|            |              | The compiled Quartus 17.0 hardware project is     |

|            |              | stored in the internal QSPI flash together with   |

|            |              | the U-Boot. The Linux distribution is loaded from |

|            |              | SD-Card by U-Boot.                                |

|            |              | The hardware project can be used for board        |

|            |              | testing as it implements the main hardware        |

|            |              | interfaces. The hardware project is generatred    |

|            | 1            | interfaces. The hardware project is generatied    |

| 1                                                                  |

|--------------------------------------------------------------------|

| with the Quartus Platform Designer QSYS Pro                        |

| and then embedded as block symbol file into the                    |

| top level wrapper. The block design hardware file                  |

| contains the following IPs:                                        |

|                                                                    |

| Arria10 Hard Processor IP core                                     |

|                                                                    |

|                                                                    |

| FPGA fabric                                                        |

| <ul> <li>Memory interface connected to</li> </ul>                  |

| FPGA fabric (x40, 4 GB)                                            |

| <ul> <li>HPS to FPGA memory interface</li> </ul>                   |

| (AXI)                                                              |

| <ul> <li>HPS IO/s connected to FPGA</li> </ul>                     |

| fabric (SD, I2C, GPIO)                                             |

| Arria10 External Memory Interface Hard                             |

| IP (x72, 8GB)                                                      |

| <ul> <li>Arria10 External Memory Interface Hard</li> </ul>         |

|                                                                    |

| IP (x40, 4GB)                                                      |

| LED (and-connected) to "calibration                                |

| done" output of memory controllers for                             |

| visual DRAM operational test                                       |

| <ul> <li>Address Span Extender</li> </ul>                          |

| <ul> <li>Needed for accessing 16 GB total</li> </ul>               |

| system memory from HPS                                             |

| Arria10 Hard IP for PCI Express                                    |

| <ul> <li>Connected to AMC Port 4-7</li> </ul>                      |

| <ul> <li>Configuration: Endpoint, Gen3,</li> </ul>                 |

| x4, Avalon MM 128bit                                               |

|                                                                    |

| SGMII Subsystem for 1000Base-X                                     |

| Ethernet                                                           |

| <ul> <li>Connected to HPS EMAC0 and</li> </ul>                     |

| AMC Backplane Port 0                                               |

| <ul> <li>Connected to HPS EMAC1 and</li> </ul>                     |

| AMC Backplane Port 1                                               |

| PIO (Parallel IO) IP                                               |

| <ul> <li>Connected to HA/LA/HB Pins on</li> </ul>                  |

| FMC                                                                |

| <ul> <li>Connected to LVDS Trigger Lines</li> </ul>                |

| on AMC Port 17-20                                                  |

| Reset and Clocking IPs                                             |

|                                                                    |

| The compiled Linux distribution contains drivers                   |

| to access and test the hardware:                                   |

| to access and test the naroware.                                   |

| • Full range memory access (using 2 GB                             |

|                                                                    |

| windows)                                                           |

| Ethernet on both SGMII Ports     ODE Assess on DIO for FMC 1/O and |

| GPIO Access on PIO for FMC I/O and                                 |

| backplane I/O loopback testing                                     |

| <ul> <li>Kernel I2C driver for reading &amp; editing</li> </ul>    |

| FMC EEPROM records                                                 |

| <ul> <li>Kernel I2C driver for PLL's and Clock</li> </ul>          |

| Distribution Multiplexer                                           |

| [          |     |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |     | <ul> <li>On request, the following example projects can be provided by N.A.T.</li> <li>Transceiver Loopback Application (FMC Port DP0-DP9, AMC Ports 0-17) BER validation with Transceiver Toolkit</li> <li>NAT-FMC-PoE-4GigE example application, with 6x Soft EMAC to SGMII connected to HPS via Avalon Bus</li> </ul>                                                                                                |

|            |     | Clock Distribution System. Differential HSTL<br>1.8V Clock Capable Output Pin.                                                                                                                                                                                                                                                                                                                                          |

| GPIO0_IO19 | G21 | Positive Clock Output (PL_CLK_OUT0_N) from<br>Clock Switch. See Section<br>Board Support Package<br>The board support package is a combination of<br>hardware and software logic which is generated<br>by Intel Design Sofware Quartus Prime Pro 17.0<br>This tool can be download at the IntelFPGA<br>Download Center. The BSP is production<br>programmed and delivered with the NAMC-<br>ARRIA10-FMC hardware board. |

|            |     | <ul> <li>The board support package contains the following items:</li> <li>Quartus 17.0 Example Project, Block Design Level, QSYS</li> <li>Linux Distribution on SD Card</li> <li>Instructions how to generate &amp; compile everything (Yocto 2.4.2)</li> </ul>                                                                                                                                                         |

|            |     | The compiled Quartus 17.0 hardware project is stored in the internal QSPI flash together with the U-Boot. The Linux distribution is loaded from SD-Card by U-Boot.                                                                                                                                                                                                                                                      |

|            |     | The hardware project can be used for board testing as it implements the main hardware interfaces. The hardware project is generatred with the Quartus Platform Designer QSYS Pro and then embedded as block symbol file into the top level wrapper. The block design hardware file contains the following IPs:                                                                                                          |

|            |     | <ul> <li>Arria10 Hard Processor IP core         <ul> <li>EMAC0, EMAC1 connected to</li> <li>FPGA fabric</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                          |

| GPIO0_IO20       F19       FPGA_RSTn External Reset Input, Active L<br>On SX Device this signal is connected to H<br>warm reset         GPIO0_IO21       G19       Single Ended Clock input from System PL<br>(Output 2_P). This always has the same<br>frequency as HPS clock. Default = 25 MH<br>(Output 2_P). This always has the same<br>frequency as HPS clock. Default = 25 MH<br>Clock Switch. See Section<br>Board Support Package         GPIO0_IO22       F22       Positive Clock Input (PL_CLK_IN0_P) from<br>Clock Switch. See Section<br>Board Support Package         The board support package is a combinatic<br>hardware and software logic which is gener<br>by Intel Design Sofware Quartus Prime Pro<br>This tool can be download at the Intelf<br>Download Center. The BSP is product<br>programmed and delivered with the NA<br>ARRIA10-FMC hardware board.         The board support package contains<br>following items:       • Quartus 17.0 Example Project, Block<br>Design Level, QSYS         Linux Distribution on SD Card       • Instructions how to generate & comp<br>everything (Yocto 2.4.2)         The compiled Quartus 17.0 hardware projes<br>stored in the internal QSPI flash together<br>the U-Boot. The Linux distribution is loaded<br>SD-Card by U-Boot.         The hardware project can be used for b |            |     | <ul> <li>Transceiver Loopback Application (FMC<br/>Port DP0-DP9, AMC Ports 0-17) BER<br/>validation with Transceiver Toolkit</li> <li>NAT-FMC-PoE-4GigE example<br/>application, with 6x Soft EMAC to<br/>SGMII connected to HPS via Avalon<br/>Bus</li> <li>Clock Distribution System. Differential HSTL<br/>1.8V Clock Capable Output Pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Output 2_P). This always has the same<br>frequency as HPS clock. Default = 25 MHGPIO0_IO22F22Positive Clock Input (PL_CLK_IN0_P) from<br>Clock Switch. See Section<br>Board Support Package<br>The board support package is a combination<br>hardware and software logic which is gener<br>by Intel Design Sofware Quartus Prime Pro<br>This tool can be download at the Intelf<br>Download Center. The BSP is produc<br>programmed and delivered with the NA<br>ARRIA10-FMC hardware board.The board support package contains<br>following items:<br>• Quartus 17.0 Example Project, Block<br>Design Level, QSYS<br>• Linux Distribution on SD Card<br>• Instructions how to generate & comp<br>everything (Yocto 2.4.2)The compiled Quartus 17.0 hardware project<br>stored in the internal QSPI flash together<br>the U-Boot.<br>The Linux distribution is loaded is<br>SD-Card by U-Boot.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GPIO0_IO20 | F19 | FPGA_RSTn External Reset Input, Active Low.<br>On SX Device this signal is connected to HPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Clock Switch. See Section<br>Board Support Package<br>The board support package is a combination<br>hardware and software logic which is genere<br>by Intel Design Sofware Quartus Prime Pro<br>This tool can be download at the Intelf<br>Download Center. The BSP is product<br>programmed and delivered with the NA<br>ARRIA10-FMC hardware board.<br>The board support package contains<br>following items:<br>• Quartus 17.0 Example Project, Block<br>Design Level, QSYS<br>• Linux Distribution on SD Card<br>• Instructions how to generate & comp<br>everything (Yocto 2.4.2)<br>The compiled Quartus 17.0 hardware project<br>stored in the internal QSPI flash together<br>the U-Boot. The Linux distribution is loaded is<br>SD-Card by U-Boot.<br>The hardware project can be used for b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GPIO0_IO21 | G19 | Single Ended Clock input from System PLL<br>(Output 2_P). This always has the same<br>frequency as HPS clock. Default = 25 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| interfaces. The hardware project is genera<br>with the Quartus Platform Designer QSYS<br>and then embedded as block symbol file into                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPIO0_IO22 | F22 | <ul> <li>Positive Clock Input (PL_CLK_IN0_P) from<br/>Clock Switch. See Section<br/>Board Support Package</li> <li>The board support package is a combination of<br/>hardware and software logic which is generated<br/>by Intel Design Sofware Quartus Prime Pro 17.0<br/>This tool can be download at the IntelFPGA<br/>Download Center. The BSP is production<br/>programmed and delivered with the NAMC-<br/>ARRIA10-FMC hardware board.</li> <li>The board support package contains the<br/>following items: <ul> <li>Quartus 17.0 Example Project, Block<br/>Design Level, QSYS</li> <li>Linux Distribution on SD Card</li> <li>Instructions how to generate &amp; compile<br/>everything (Yocto 2.4.2)</li> </ul> </li> <li>The compiled Quartus 17.0 hardware project is<br/>stored in the internal QSPI flash together with<br/>the U-Boot. The Linux distribution is loaded from<br/>SD-Card by U-Boot.</li> <li>The hardware project can be used for board<br/>testing as it implements the main hardware<br/>interfaces. The hardware project is generatred<br/>with the Quartus Platform Designer QSYS Pro<br/>and then embedded as block symbol file into the<br/>top level wrapper. The block design hardware file<br/>contains the following IPs: <ul> <li>Arria10 Hard Processor IP core</li> <li>EMAC0, EMAC1 connected to</li> </ul> </li> </ul> |

|            |     | <ul> <li>Transceiver Loopback Application (FMC<br/>Port DP0-DP9, AMC Ports 0-17) BER<br/>validation with Transceiver Toolkit</li> <li>NAT-FMC-PoE-4GigE example<br/>application, with 6x Soft EMAC to<br/>SGMII connected to HPS via Avalon<br/>Bus</li> <li>Clock Distribution System. Differential HSTL<br/>1.8V Clock Capable Input Pin</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO0_IO23 | G22 | <ul> <li>Negative Clock Input (PL_CLK_IN0_N) from<br/>Clock Switch. See Section<br/>Board Support Package</li> <li>The board support package is a combination of<br/>hardware and software logic which is generated<br/>by Intel Design Sofware Quartus Prime Pro 17.0<br/>This tool can be download at the IntelFPGA<br/>Download Center. The BSP is production<br/>programmed and delivered with the NAMC-<br/>ARRIA10-FMC hardware board.</li> <li>The board support package contains the<br/>following items:         <ul> <li>Quartus 17.0 Example Project, Block<br/>Design Level, QSYS</li> <li>Linux Distribution on SD Card</li> <li>Instructions how to generate &amp; compile<br/>everything (Yocto 2.4.2)</li> </ul> </li> <li>The compiled Quartus 17.0 hardware project is<br/>stored in the internal QSPI flash together with<br/>the U-Boot. The Linux distribution is loaded from<br/>SD-Card by U-Boot.</li> <li>The hardware project can be used for board<br/>testing as it implements the main hardware<br/>interfaces. The hardware project is generatred<br/>with the Quartus Platform Designer QSYS Pro<br/>and then embedded as block symbol file into the<br/>top level wrapper. The block design hardware file<br/>contains the following IPs:         <ul> <li>Arria10 Hard Processor IP core</li> <li>EMACO, EMAC1 connected to<br/>FPGA fabric</li> <li>Memory interface connected to<br/>FPGA fabric</li> <li>HPS to FPGA memory interface<br/>(AXI)</li> <li>HPS to Connected to FPGA<br/>fabric (SD, 12C, GPIO)</li> </ul> </li> </ul> |

| <ul> <li>Arria10 External Memory Interface Hard<br/>IP (x72, 8GB)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Arria10 External Memory Interface Hard<br/>IP (x40, 4GB)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>LED (and-connected) to "calibration</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| done" output of memory controllers for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| visual DRAM operational test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Address Span Extender                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |