### The Embedded I/O Company

# **TPMC395**

### Conduction Cooled, Four Channel 10/100/1000 Mbit/s **Ethernet**

Version 1.0

### **User Manual**

Issue 1.0.0 December 2021

Ehlbeek 15a 30938 Burgwedel fon 05139-9980-0 fax 05139-9980-49

www.powerbridge.de info@powerbridge.de

#### **TEWS TECHNOLOGIES GmbH**

Phone: +49 (0) 4101 4058 0 Fax: +49 (0) 4101 4058 19 e-mail: info@tews.com www.tews.com

Am Bahnhof 7 25469 Halstenbek, Germany

#### **TPMC395-10R**

Conduction Cooled, Four Channel 10/100/1000 Mbit/s Ethernet, Intel I210IT, P14 Back I/O

(RoHS compliant)

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However, TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### ©2021 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description   | Date          |

|-------|---------------|---------------|

| 1.0.0 | Initial issue | December 2021 |

## **Table of Contents**

| 1 | PRODUCT DESCRIPTION                              | 6  |

|---|--------------------------------------------------|----|

| 2 | TECHNICAL SPECIFICATION                          | 7  |

| 3 | HANDLING AND OPERATION INSTRUCTIONS              | 8  |

|   | 3.1 ESD Protection                               | 8  |

|   | 3.2 Power Dissipation                            |    |

| 4 | PCI INTERFACE                                    | 9  |

|   | 4.1 TPMC395 PCI Device Topology                  | 9  |

|   | 4.2 TPMC395 PCI Memory and I/O Size Requirements | 9  |

|   | 4.3 I210 PCI Identifiers                         | 10 |

|   | 4.4 I210 PCI Base Address Register Configuration | 10 |

| 5 | ETHERNET INTERFACE STATUS LEDS                   | 11 |

| 6 | PIN ASSIGNMENT - I/O CONNECTORS                  | 12 |

|   | 6.1 Back I/O P14 Connector                       | 12 |

## **List of Figures**

| FIGURE 1-1: BLOCK DIAGRAM                               | 6  |

|---------------------------------------------------------|----|

| FIGURE 4-1: TPMC395 PCI DEVICE TOPOLOGY                 |    |

|                                                         |    |

|                                                         |    |

|                                                         |    |

|                                                         |    |

| List of Tables                                          |    |

| LIST OF TABLES                                          |    |

| TABLE 2-1: TECHNICAL SPECIFICATION                      |    |

| TABLE 4-1: TPMC395 PCI MEMORY AND I/O SIZE REQUIREMENTS | 9  |

| TABLE 4-2: I210 PCI IDENTIFIERS                         | 10 |

| TABLE 4-3: I210 PCI BASE ADDRESS REGISTER CONFIGURATION | 10 |

| TABLE 5-1: STATUS LED                                   | 11 |

TABLE 6-1: BACK I/O P14 CONNECTOR......12

## 1 Product Description

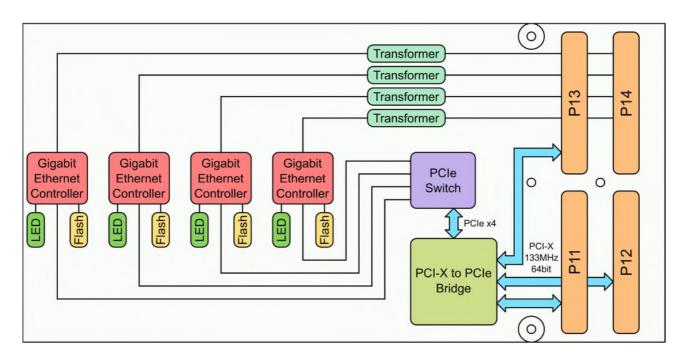

The TPMC395 is a Conduction Cooled PCI Mezzanine Card (CCPMC) compatible module providing a four channel Ethernet 10Base-T / 100Base-TX / 1000Base-T interface.

A transparent 64 bit, up to 133 MHz PCI-X/PCI to PCIe Bridge and a PCIe Switch provide access to the Intel I210IT Gigabit Ethernet controllers. Each Ethernet interface supports 10, 100 and 1000 Mbit/s transmission rates and is equipped with a 16 Mbit Serial Flash to support PXE and iSCSI boot.

The four Ethernet interfaces of the TPMC395 are capable of performing an auto negotiation algorithm which allows both link-partners to determine the best link-parameters. The TPMC395 supports IEEE 1588/802.1AS Precision Time Protocol (PTP) and IEEE 802.1Qav Audio/Video Bridging (AVB) traffic shaping (with software extensions).

The TPMC395-10R routes four Ethernet ports to the Back I/O P14 connector.

All ports are galvanically isolated from the Ethernet controllers and LEDs on the board indicate the different network activities.

The module meets the requirements to operate in extended temperature range from -40°C to +85°C.

#### **Software Support:**

- Software support for Intel I210IT at www.intel.com

- o For operating systems not supported by Intel, please contact TEWS.

Figure 1-1: Block Diagram

## 2 Technical Specification

| PMC Interface        |                                                                                                                                                                            |  |  |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Mechanical Interface | Conduction Cooled PCI Mezzanine Card (CCPMC) Interface conforming to IEEE P1386/P1386.1 and ANSI/VITA 20 Standard single-width (143.75 mm x 74 mm)                         |  |  |  |  |  |

| Electrical Interface | 64 bit PCI (Specification 3.0) up to 66 MHz and 64 bit PCI-X (Specification 2.0a) up to 133 MHz compliant interface conforming to 3.3V PCI signaling with 5V I/O tolerance |  |  |  |  |  |

| On Board Devices                    |                                        |  |  |  |  |

|-------------------------------------|----------------------------------------|--|--|--|--|

| PCI/PCI-X to PCIe Bridge            | PI7C9X130 (Diodes Incorporated)        |  |  |  |  |

| PCIe Switch                         | PI7C9X2G608GP (Diodes Incorporated)    |  |  |  |  |

| Gigabit Ethernet Controllers        | For each interface: I210-IT (Intel)    |  |  |  |  |

| 16 Mbit Serial Flashes for Boot ROM | For each interface: W25Q16JV (Winbond) |  |  |  |  |

| I/O Interface      |                                              |  |  |  |  |

|--------------------|----------------------------------------------|--|--|--|--|

| Number of Channels | 4                                            |  |  |  |  |

| I/O Standards      | 1000Base-T<br>100Base-TX<br>10Base-T         |  |  |  |  |

| I/O Connector      | Back I/O P14 (Molex 714362864 or compatible) |  |  |  |  |

| Physical Data      |                                                                                     |                                                                                                                                                                                                                                                                             |  |  |  |

|--------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Power Requirements | 1000mA typical @ +5V (four channel, no link) app. additional 10mA to 100mA per link |                                                                                                                                                                                                                                                                             |  |  |  |

| Temperature Range  | Operating<br>Storage                                                                | -40°C to +85°C<br>-40°C to +85°C                                                                                                                                                                                                                                            |  |  |  |

| MTBF               | MIL-HDBK-217I<br>The MTBF calcu<br>component sup                                    | nown are based on calculation according to MIL-HDBK-217F and F Notice 2; Environment: $G_B$ 20°C.  ulation is based on component FIT rates provided by the pliers. If FIT rates are not available, MIL-HDBK-217F and F Notice 2 formulas are used for FIT rate calculation. |  |  |  |

| Humidity           | 5 – 95 % non-condensing                                                             |                                                                                                                                                                                                                                                                             |  |  |  |

| Weight             | 69 g                                                                                |                                                                                                                                                                                                                                                                             |  |  |  |

Table 2-1: Technical Specification

## 3 Handling and Operation Instructions

### 3.1 ESD Protection

This CCPMC module is sensitive to static electricity.

Packing, unpacking and all other module handling has to be done with appropriate care.

## 3.2 Power Dissipation

This CCPMC module requires adequate conduction cooling!

## 4 PCI Interface

## 4.1 TPMC395 PCI Device Topology

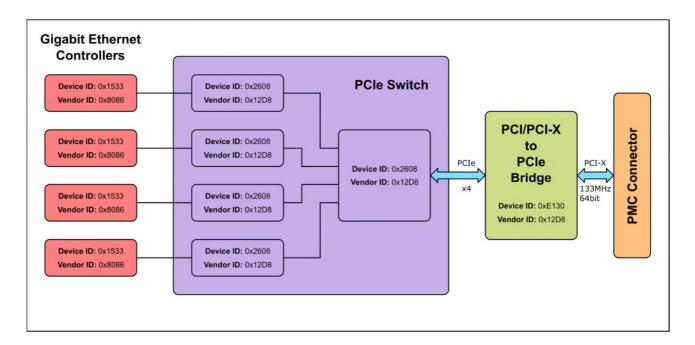

The TPMC395 uses four Gigabit Ethernet Controllers (Intel I210-IT) each communicating via a PCIe Rev. 2.1 compliant x1 Interface.

To be able to access the Ethernet controllers they are connected to the x1 Downstream Ports of a PCle Switch (Diodes Incorporated PI7C9X2G608GP).

The x4 Upstream Port of the PCIe Switch is connected to a PCI/PCI-X to PCIe Bridge (Diodes Incorporated PI7C9X130) which communicates with the host system.

Figure 4-1: TPMC395 PCI Device Topology

## 4.2 TPMC395 PCI Memory and I/O Size Requirements

| PCI Space Mapping | Four Channel<br>(Byte) | Two Channel<br>(Byte) |

|-------------------|------------------------|-----------------------|

| MEM               | 4M                     | 2M                    |

| I/O               | 16K                    | 8K                    |

Table 4-1: TPMC395 PCI Memory and I/O Size Requirements

### 4.3 I210 PCI Identifiers

| Vendor-ID           | 0x8086 (Intel)                 |  |  |  |  |

|---------------------|--------------------------------|--|--|--|--|

| Device-ID           | 0x1533 (I210-IT copper only)   |  |  |  |  |

| Class Code          | 0x020000 (Ethernet Controller) |  |  |  |  |

| Subsystem Vendor-ID | 0xFFFF                         |  |  |  |  |

| Subsystem Device-ID | 0x0000                         |  |  |  |  |

Table 4-2: I210 PCI Identifiers

## 4.4 I210 PCI Base Address Register Configuration

| PCI Base Address Register<br>(Offset in PCI<br>Configuration Space) | PCI<br>Space<br>Mapping | Size<br>(Byte) | Description                      |

|---------------------------------------------------------------------|-------------------------|----------------|----------------------------------|

| 0 (0x10)                                                            | MEM                     | 128K           | Internal Registers               |

| 1 (0x14)                                                            | -                       | -              | -                                |

| 2 (0x18)                                                            | I/O                     | 32             | Internal Registers via I/O Space |

| 3 (0x1C)                                                            | MEM                     | 16K            | MSI-X                            |

Table 4-3: I210 PCI Base Address Register Configuration

## 5 Ethernet Interface Status LEDs

The TPMC395 provides an individual Status LED for every Ethernet Interface. Due to the fact that CCPMCs are mounted upside-down on the carrier card the Status LEDs are visible on the back side of the TPMC395. A marking is placed close to each Status LED to indicate the Ethernet Port it corresponds to.

See table below for more details:

| Status LED | Description                                             |  |  |  |

|------------|---------------------------------------------------------|--|--|--|

| OFF        | No cable is connected or no link is established         |  |  |  |

| ON         | A link is established                                   |  |  |  |

| BLINKING   | Activity (the Ethernet Port transmits or receives data) |  |  |  |

Table 5-1: Status LED

## 6 Pin Assignment – I/O Connectors

## 6.1 Back I/O P14 Connector

| Signal              | Pin |      | <del></del> |                                            | Ţ            | Pin | Signal              |

|---------------------|-----|------|-------------|--------------------------------------------|--------------|-----|---------------------|

| TERM_PLANE          | 63  | ][   | ╫╌ѭ         | ╬╬                                         | ħL           | 64  | TERM_PLANE          |

| ETHERNET_2_TX3/RX3- | 61  | ]]   | <u> </u>    |                                            |              | 62  | ETHERNET_1_TX3/RX3- |

| ETHERNET_2_TX3/RX3+ | 59  | الا  | ΠД          |                                            | IJĽ          | 60  | ETHERNET_1_TX3/RX3+ |

| TERM_PLANE          | 57  |      |             |                                            | 116          | 58  | TERM_PLANE          |

| ETHERNET_2_TX2/RX2- | 55  |      | II 4        | III⊑ I                                     | [            | 56  | ETHERNET_1_TX2/RX2- |

| ETHERNET_2_TX2/RX2+ | 53  | 4    | II d        | ll⊯ l                                      |              | 54  | ETHERNET_1_TX2/RX2+ |

| TERM_PLANE          | 51  | 4    | II d        |                                            | <b>I</b> Iþ  | 52  | TERM_PLANE          |

| ETHERNET_1_TX0/RX0- | 49  | 4    | II 4        | III⊪ I                                     | <b>I</b> IÞ  | 50  | ETHERNET_1_TX1/RX1- |

| TERM_PLANE          | 47  | 4    | II Ħ        | <b>   </b>                                 | <b>I</b> IÞ  | 48  | TERM_PLANE          |

| ETHERNET_1_TX0/RX0+ | 45  | 4    | II ¶        | III₽III                                    | <b>l</b> lÞ  | 46  | ETHERNET_1_TX1/RX1+ |

| TERM_PLANE          | 43  | 9    | ll fi       |                                            |              | 44  | TERM_PLANE          |

| TERM_PLANE          | 41  | ]]   |             |                                            |              | 42  | TERM_PLANE          |

| ETHERNET_2_TX0/RX0- | 39  | الإا | IJ          |                                            | IJĽ          | 40  | ETHERNET_2_TX1/RX1- |

| TERM_PLANE          | 37  |      | IJÄ         |                                            | IJĽ          | 38  | TERM_PLANE          |

| ETHERNET_2_TX0/RX0+ | 35  |      |             |                                            | 116          | 36  | ETHERNET_2_TX1/RX1+ |

| TERM_PLANE          | 33  |      | II d        |                                            | [            | 34  | TERM_PLANE          |

| TERM_PLANE          | 31  | 4    | II d        | <b>                                   </b> | <b>I</b> II  | 32  | TERM_PLANE          |

| ETHERNET_3_TX0/RX0- | 29  | 4    | II d        | ₩                                          | <b> </b>   þ | 30  | ETHERNET_3_TX1/RX1- |

| TERM_PLANE          | 27  | 4    | II 4        | III⊫ I                                     | <b>I</b> IÞ  | 28  | TERM_PLANE          |

| ETHERNET_3_TX0/RX0+ | 25  | 4    | II ij       | III₽II                                     | <b>l</b> lÞ  | 26  | ETHERNET_3_TX1/RX1+ |

| TERM_PLANE          | 23  | 4    | II Я        | IIIF I                                     | llÞ          | 24  | TERM_PLANE          |

| TERM_PLANE          | 21  | ]    | 11 3        |                                            |              | 22  | TERM_PLANE          |

| ETHERNET_4_TX0/RX0- | 19  | ונ   | 11 ]        |                                            | ll!          | 20  | ETHERNET_4_TX1/RX1- |

| TERM_PLANE          | 17  | וג   | ΠД          |                                            | IJĽ          | 18  | TERM_PLANE          |

| ETHERNET_4_TX0/RX0+ | 15  | الا  | ΠД          |                                            | IJĽ          | 16  | ETHERNET_4_TX1/RX1+ |

| TERM_PLANE          | 13  |      |             |                                            | 116          | 14  | TERM_PLANE          |

| ETHERNET_4_TX2/RX2- | 11  |      | II d        |                                            | 116          | 12  | ETHERNET_3_TX2/RX2- |

| ETHERNET_4_TX2/RX2+ | 9   | 4    | II d        | ll⊪ I                                      |              | 10  | ETHERNET_3_TX2/RX2+ |

| TERM_PLANE          | 7   | 4    | II d        |                                            | l þ          | 8   | TERM_PLANE          |

| ETHERNET_4_TX3/RX3- | 5   |      |             |                                            | <b>I</b> Iþ  | 6   | ETHERNET_3_TX3/RX3- |

| ETHERNET_4_TX3/RX3+ | 3   | ГТ   | ₩.          | ╓╌┼                                        | 儿            | 4   | ETHERNET_3_TX3/RX3+ |

| TERM_PLANE          | 1   |      | H           |                                            |              | 2   | TERM_PLANE          |

Table 6-1: Back I/O P14 Connector