# **TPMC851**

# **Multifunction I/O** (16 bit ADC/DAC, TTL I/O, Counter)

Version 1.0

### **User Manual**

Issue 1.0.9 September 2014

#### **TPMC851-10R**

Multifunction I/O

(16 bit ADC/DAC, TTL I/O, Counter)

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP\_RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

#### ©2014 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                                                                                      | Date           |

|-------|--------------------------------------------------------------------------------------------------|----------------|

| 1.0   | Initial Issue                                                                                    | May 2004       |

| 1.1   | Added ADC power-up note                                                                          | January 2005   |

| 1.2   | Correction Interrupt Control Register ICR, Summarization of Important Notes                      | February 2006  |

| 1.3   | New address TEWS LLC                                                                             | September 2006 |

| 1.4   | Changed PCI9030 Local Configuration Clarified Sequencer Start / Stop Control in ADCSEQCONT       | September 2006 |

| 1.5   | Added note to ADC Control Register                                                               | October 2006   |

| 1.0.6 | New notation for HW Engineering Documentation Releases                                           | March 2009     |

| 1.0.7 | Corrected DAC Data Register Reset Value to 0x0000                                                | January 2010   |

| 1.0.8 | General Revision                                                                                 | August 2014    |

| 1.0.9 | "PCI Base Address 2 for Local Address Space 0" initial value corrected in Table "PCI9030 Header" | September 2014 |

# **Table of Contents**

| 1 | PRODUCT DESCRIPTION                                                   | 8          |

|---|-----------------------------------------------------------------------|------------|

| 2 | TECHNICAL SPECIFICATION                                               | 10         |

| 3 | LOCAL SPACE ADDRESSING                                                |            |

|   | 3.1 PCI9030 Local Space Configuration                                 |            |

|   | 3.2 Local Register Address Space                                      |            |

|   | 3.2.1 Analog Input Registers                                          |            |

|   | 3.2.1.1 ADC Control Register ADCCONT (Offset 0x0000)                  |            |

|   | 3.2.1.2 ADC Data Register ADCDATA (Offset 0x0004)                     |            |

|   | 3.2.1.3 ADC Status Register ADCSTAT (Offset 0x0008)                   | 17         |

|   | 3.2.1.4 ADC Conversion Start Register ADCCONV (Offset 0x000C)         | 18         |

|   | 3.2.1.5 ADC Sequencer Control Register ADCSEQCONT (Offset 0x0010)     |            |

|   | 3.2.1.6 ADC Sequencer Status Register ADCSEQSTAT (Offset 0x0014)      |            |

|   | 3.2.1.7 ADC Sequencer Timer Register ADCSEQTIME (Offset 0x0018)       |            |

|   | 3.2.1.8 ADC Sequencer Instruction RAM (Offset 0x0020 - Offset 0x009C) |            |

|   | 3.2.2 Analog Output Registers                                         |            |

|   | 3.2.2.1 DAC Control Register DACCONT (Offset 0x00C0)                  | 24         |

|   | 3.2.2.2 DAC Sequencer Status Register DACSEQSTAT (Offset 0x00C4)      | 25         |

|   | 3.2.2.3 DAC Sequencer Timer Register DACSEQTIME (Offset 0x00C8)       |            |

|   | 3.2.2.4 DAC Data Register DACDATA 1-8 (Offset 0x00D0 - Offset 0x00EC) |            |

|   | 3.2.3 Digital I/O Registers                                           |            |

|   | 3.2.3.1 Line Direction Register LINEDIR (Offset 0x0100)               |            |

|   | 3.2.3.3 Line Debounce Time Register LINEDBT (Offset 0x0104)           |            |

|   | 3.2.3.4 Line Input Register LINEIN (Offset 0x010C)                    |            |

|   | 3.2.3.5 Line Output Register LINEOUT (Offset 0x0110)                  |            |

|   | 3.2.3.6 Line Interrupt Enable Register LINEIEN (Offset 0x0114)        | 31         |

|   | 3.2.3.7 Line Interrupt Status Register LINEIST (Offset 0x0118)        |            |

|   | 3.2.4 Counter Registers                                               |            |

|   | 3.2.4.1 Counter Preload Register CNTPRL (Offset 0x0120)               |            |

|   | 3.2.4.2 Counter Compare Register CNTCMP (Offset 0x0124)               | 33         |

|   | 3.2.4.3 Counter Data Register CNTDATA (Offset 0x0128)                 | 33         |

|   | 3.2.4.4 Counter Control Register CNTCONT (Offset 0x012C)              |            |

|   | 3.2.4.5 Counter Status Register CNTSTAT (Offset 0x0130)               |            |

|   | 3.2.4.6 Counter Command Register CNTCOM (Offset 0x0134)               | 37         |

|   | 3.2.5 Interrupt Control Register ICR (Offset 0x0140)                  |            |

|   | 3.3 ADC Sequencer Data RAM                                            |            |

|   | 3.4 ADC/DAC Calibration Data ROM                                      |            |

| 4 | PCI9030 TARGET CHIP                                                   |            |

|   | 4.1 PCI Configuration Registers (PCR)                                 | <b>4</b> 1 |

|   | 4.1.1 PCI9030 Header                                                  |            |

|   | 4.1.2 PCI Base Address Initialization                                 |            |

|   | 4.2 Local Configuration Register (LCR)                                |            |

|   | 4.3 Configuration EEPROM                                              |            |

|   | 4.4 Local Software Reset                                              |            |

| 5 | CONFIGURATION HINTS                                                   |            |

|   | 5.1 Big / Little Endian                                               | 45         |

| PROGRA      | MMING HINTS                                           | 47 |

|-------------|-------------------------------------------------------|----|

| 6.1 Data C  | orrection                                             | 47 |

| 6.1.1       | ADC Correction Formula                                | 47 |

|             | DAC Correction Formula                                |    |

| 6.2 ADC 0   | perating Modes                                        | 48 |

| 6.2.1       | Manual Mode                                           | 48 |

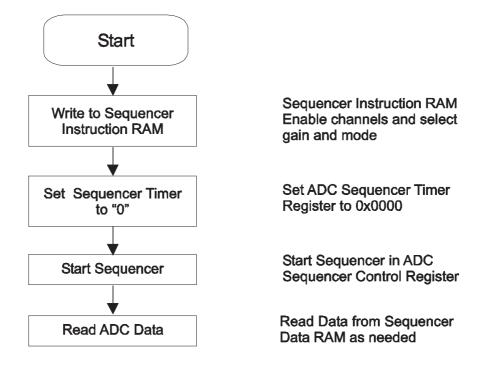

|             | Sequencer Mode                                        |    |

|             | 2.1 Sequencer Errors                                  |    |

|             | Application Examples                                  |    |

|             | 3.1 Fastest Conversion of an arbitrary Single Channel |    |

|             | 3.2 Fastest Conversion of a specific Single Channel   |    |

| 6.2.        | 3.3 Periodic Conversion of multiple Channels          | 53 |

| 6.2.        | 3.4 Continuous Conversion of multiple Channels        | 54 |

| 6.3 DAC O   | perating Modes                                        | 55 |

| 6.3.1       | Immediate Update                                      | 55 |

| 6.3.2       | Simultaneous Update                                   |    |

| 6.4 Digital | TTL I/O                                               |    |

| 6.5 Counte  | er Operating Modes                                    | 57 |

|             | Input Modes                                           |    |

|             | 1.1 Timer Mode                                        |    |

|             | 1.2 Direction Count                                   |    |

|             | 1.3 Up/Down Count                                     |    |

|             | 1.4 Quadrature Count                                  |    |

|             | Count Modes                                           |    |

|             | 2.1 Divide-by-N                                       |    |

|             | 2.2 Single Cycle                                      |    |

|             | Control Modes                                         |    |

| 6.5.        |                                                       |    |

|             | 3.2 Load Mode                                         |    |

|             | 3.3 Latch Mode                                        |    |

|             | 3.4 Gate Mode                                         |    |

|             | 3.5 Reset Mode                                        |    |

|             | Configuration Examples                                |    |

|             | 4.1 Watchdog Timer                                    |    |

|             | 4.2 Event Counting                                    |    |

| 6.5.        | · · · · · · · · · · · · · · · · · · ·                 |    |

| 6.5.        | '                                                     |    |

|             | pts                                                   |    |

|             | Interrupt Sources                                     |    |

|             | •                                                     |    |

| INSTALL     | ATION                                                 | 62 |

| 7.1 ADC Ir  | nput Wiring                                           | 62 |

|             | output Wiring                                         |    |

|             | O Interface                                           |    |

|             |                                                       |    |

| PIN ASSI    | GNMENT – I/O CONNECTOR                                | 64 |

| IMPORTA     | ANT NOTES                                             | 65 |

|             | y Conversions after Power-up                          |    |

|             | Multiployor Inputs                                    | 65 |

# **List of Figures**

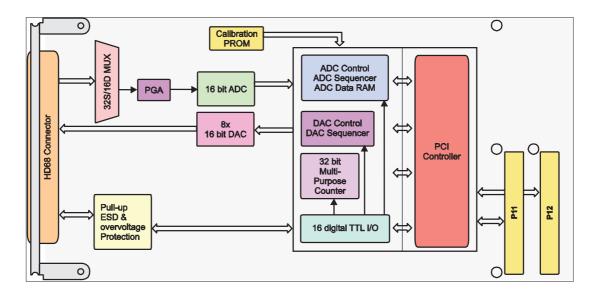

| FIGURE 1-1:BLOCK DIAGRAM                                            | 9  |

|---------------------------------------------------------------------|----|

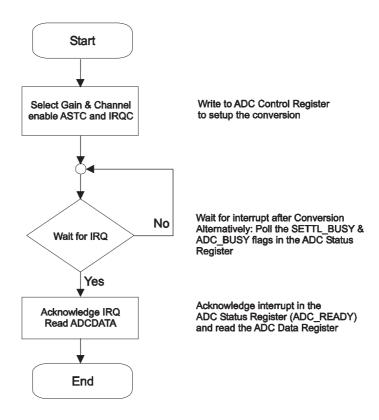

| FIGURE 6-1: FLOW: FASTEST CONVERSION OF AN ARBITRARY SINGLE CHANNEL | 51 |

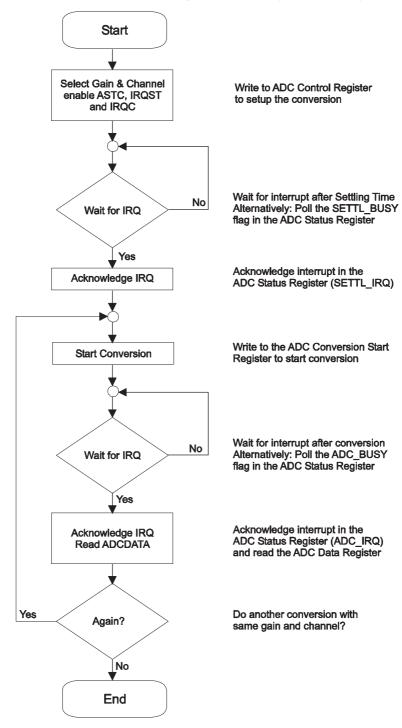

| FIGURE 6-2: FLOW: FASTEST CONVERSION OF A SPECIFIC SINGLE CHANNEL   | 52 |

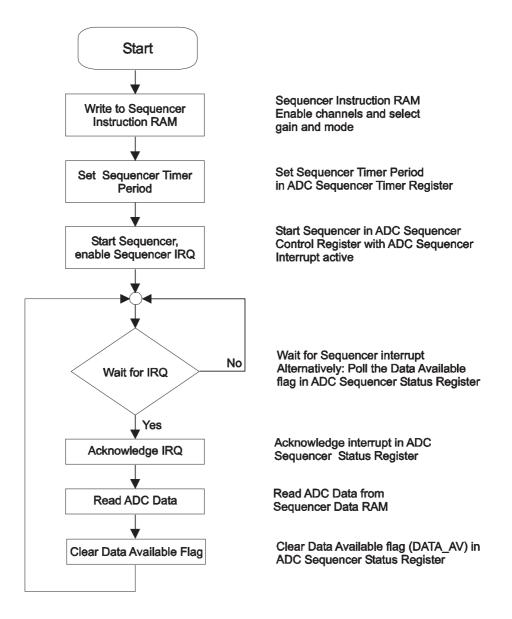

| FIGURE 6-3: FLOW: PERIODIC CONVERSION OF MULTIPLE CHANNELS          | 53 |

| FIGURE 6-4: FLOW: CONTINUOUS CONVERSION OF MULTIPLE CHANNELS        | 54 |

| FIGURE 6-5: QUADRATURE SIGNALS                                      | 58 |

| FIGURE 7-1: ADC INPUT WIRING                                        | 62 |

| FIGURE 7-2: DAC OUTPUT WIRING                                       | 63 |

| FIGURE 7-3: TTL I/O INTERFACE                                       | 63 |

| List of Tables                                                      |    |

| TABLE 2-1: TECHNICAL SPECIFICATION                                  | 11 |

| TABLE 3-1: PCI9030 LOCAL SPACE CONFIGURATION                        | 12 |

| TABLE 3-2: REGISTER WORD/BYTE ACCESSES                              | 12 |

| TABLE 3-3: REGISTER ADDRESS SPACE                                   | 13 |

| TABLE 3-4: ADC CONTROL REGISTER                                     | 15 |

| TABLE 3-5 : ADC DATA REGISTER                                       | 16 |

| TABLE 3-6: ADC DATA CODING                                          | 16 |

| TABLE 3-7: ADC STATUS REGISTER                                      | 17 |

| TABLE 3-8: ADC SEQUENCER CONTROL REGISTER                           | 19 |

| TABLE 3-9: ADC SEQUENCER STATUS REGISTER                            | 20 |

| TABLE 3-10: ERROR FLAG IRQ GENERATION                               | 20 |

| TABLE 3-11: ADC SEQUENCER TIMER REGISTER                            | 21 |

| TABLE 3-12: ADC SEQUENCER INSTRUCTION RAM REGISTER                  |    |

| TABLE 3-13: ADC SEQUENCER INSTRUCTION RAM REGISTER POSITIONS        |    |

| TABLE 3-14: DAC CONTROL REGISTER                                    |    |

| TABLE 3-15: DAC SEQUENCER STATUS REGISTER                           |    |

| TABLE 3-16: DAC SEQUENCER TIMER REGISTER                            |    |

| TABLE 3-17: DAC DATA REGISTER                                       |    |

| TABLE 3-18: DAC DATA CODING                                         |    |

| TABLE 3-19: LINE DIRECTION REGISTER                                 |    |

| TABLE 3-20: LINE DEBOUNCE ENABLE REGISTER                           |    |

| TABLE 3-21: LINE DEBOUNCE TIME REGISTER                             |    |

| TABLE 3-22: LINE INPUT REGISTER                                     |    |

| TABLE 3-23: LINE OUTPUT REGISTER                                    |    |

| TABLE 3-24: LINE INTERRUPT ENABLE REGISTER                          |    |

| TABLE 3-25: LINE INTERRUPT STATUS REGISTER                          |    |

| TABLE 3-26: COUNTER PRELOAD REGISTER                                |    |

| TABLE 3-27: COUNTER COMPARE REGISTER                                |    |

| TABLE 3-28: COUNTER DATA REGISTER                                   | 33 |

|                                                                     |    |

| TABLE 3-29: COUNTER CONTROL REGISTER                       |    |

|------------------------------------------------------------|----|

| TABLE 3-30: COUNTER STATUS REGISTER                        | 36 |

| TABLE 3-31: COUNTER COMMAND REGISTER                       | 37 |

| TABLE 3-32: INTERRUPT CONTROL REGISTER                     | 38 |

| TABLE 3-33: ADC SEQUENCER DATA RAM SPACE ADDRESS MAP       | 39 |

| TABLE 3-34: ADC/DAC CALIBRATION ROM DATA SPACE ADDRESS MAP | 40 |

| TABLE 4-1: PCI9030 HEADER                                  | 41 |

| TABLE 4-2: PCI9030 PCI BASE ADDRESS USAGE                  | 42 |

| TABLE 4-3: PCI9030 LOCAL CONFIGURATION REGISTER            | 43 |

| TABLE 4-4: CONFIGURATION EEPROM TPMC851-10R                | 44 |

| TABLE 5-1: LOCAL BUS LITTLE/BIG ENDIAN                     |    |

| TABLE 6-1: SEQUENCER ERRORS                                | 50 |

| TABLE 6-2: DAC LOAD MODES                                  | 55 |

| TABLE 6-3: INPUT MODES                                     | 57 |

| TABLE 6-4: CLOCK PRESCALER                                 | 57 |

| TABLE 6-5: COUNT DIRECTIONS                                | 57 |

| TABLE 6-6: INPUT CONTROL MODE EVENTS                       |    |

| TABLE 6-7: GATE MODE                                       | 59 |

| TABLE 6-8: INTERRUPT SOURCES                               | 61 |

| TABLE 8-1: PIN ASSIGNMENT I/O CONNECTOR                    | 64 |

# 1 Product Description

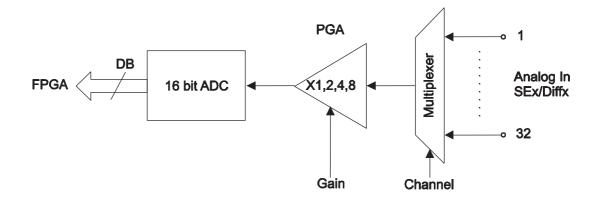

The TPMC851 combines 32 single ended / 16 differential channels of 16 bit multiplexed analog input, 8 channels of 16 bit analog output, 16 digital I/O lines and a 32 bit multi-purpose counter on a standard single-width PMC module.

A 16 bit ADC converts 32 single-ended or 16 differential multiplexed ADC input channels. The data acquisition and conversion time is up to 1.25µs without channel/gain change and up to 17.25µs with channel/gain change. The input multiplexer of the A/D circuit offers analog overvoltage protection of up to 70Vpp. A programmable gain amplifier allows gains of 1, 2, 4 or 8 resulting in input voltage ranges of ±10V, ±5V, ±2.5V or ±1.25V.

The ADC part of the TPMC851 can operate in Manual Mode or Sequencer Mode:

#### Manual Mode

In Manual Mode the multiplexer, programmable gain amplifier and the converter are fully controlled by the user. A conversion for a selected channel / gain can be started automatically after the settling time has elapsed, or manually by the user.

#### Sequencer Mode

In Sequencer Mode each of the A/D channels can be independently enabled and configured for the sequencer. The sequencer can run continuously, at specific time intervals, or it may be triggered by an external event. Conversion data is stored in a data RAM.

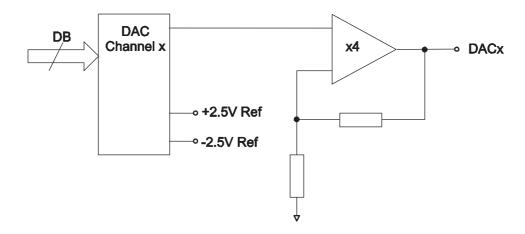

The 8 analog output channels are realized by eight 16 bit digital to analog converters (DACs). The conversion time is 10  $\mu$ s. An operational amplifier drives the full-scale range of  $\pm 10$ V and is capable to drive high capacitive loads. Similar to the analog inputs a sequencer can control the analog outputs. Following operation modes are available:

- Immediate Update: Updates the DAC output immediately when new data is written to the DAC channel.

- Simultaneous Update: DAC data is buffered and all DAC outputs are updated simultaneously on a trigger event:

- Manual Update: Updates all DAC outputs on a manual event (register write)

- o Trigger Update: Updates all DAC outputs on a external event

- o Sequencer Update: Updates all DAC outputs after the sequencer timer has elapsed

Each TPMC851 is factory calibrated. The calibration data is stored in an EEPROM unique to each TPMC851.

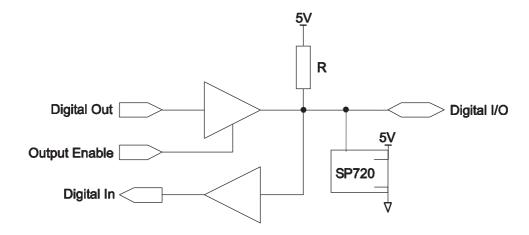

The 16 digital TTL tri-state I/O lines with  $4.7k\Omega$  pull up resistors are ESD protected and protected against overvoltage. All 16 lines can be individually programmed as input or output, and can generate an interrupt on negative and positive transitions. Each input has an electronic debounce circuit to prevent short spikes on the input lines to cause an interrupt. The digital inputs can supply the external signals for the ADC and DAC sequencer and the 32 bit counter.

Additionally the TPMC851 offers a 32 bit multi-purpose counter. The counter includes a 32 bit preload register and a 32 bit compare register. The 32 bit counter can be fed with an internal clock or with an external signal supplied by the digital inputs. The 4 counter input modes determine the interpretation of the input signals. Additionally 3 count modes, which describe the behavior of the counter, and 4 control modes are available.

#### · Counter input modes:

- o Internal clock with prescaler

- o Up/Down count: first counter input counts up, second input counts down

- o Direction count: first counter input counts, second input sets count direction

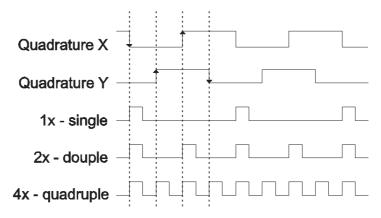

- Quadrature count with 1x, 2x or 4x resolution multiplier

#### · Count modes:

- Cycling Counter: normal wrap-around count mode

- Divide-by-N: counter is reloaded from the preload register upon a borrow or carry

- Single Cycle: counter stops upon a borrow or carry

#### · Control Modes:

- Load on Control: counter is reloaded from the preload register

- o Latch on Control: counter value is latched

- o Gate on Control: counter input is gated

- o Reset on Control: counter is reset

Figure 1-1: Block Diagram

# 2 Technical Specification

| PMC Interface                |                                                            |  |  |

|------------------------------|------------------------------------------------------------|--|--|

| Mechanical Interface         | PCI Mezzanine Card (PMC) Interface                         |  |  |

|                              | Single Size                                                |  |  |

| Electrical Interface         | PCI Rev. 2.2 compliant                                     |  |  |

|                              | 33 MHz / 32 bit PCI                                        |  |  |

|                              | 3.3V and 5V PCI Signaling Voltage                          |  |  |

| On Board Devices             |                                                            |  |  |

| PCI Target Chip              | PCI9030 (PLX Technology)                                   |  |  |

| ADC                          | AD7663                                                     |  |  |

| DAC                          | DAC7644                                                    |  |  |

| Analog Input                 |                                                            |  |  |

| Number of Analog Inputs      | 32 single-ended or 16 differential channels                |  |  |

| Input Gain Amplifier         | Programmable for gain 1, 2, 4 and 8                        |  |  |

| Input Voltage Range          | ±10V for gain = 1                                          |  |  |

|                              | $\pm 5$ V for gain = 2                                     |  |  |

|                              | ±2.5V for gain = 4                                         |  |  |

|                              | ±1.25V for gain = 8                                        |  |  |

| Input Overvoltage Protection | 70Vpp                                                      |  |  |

| Calibration Data             | Calibration data for gain and offset correction in ID PROM |  |  |

| Resolution                   | 16 bit with no missing codes                               |  |  |

| Conversion Time              | 1.25µs without channel/gain change                         |  |  |

|                              | 17.25µs with channel/gain change                           |  |  |

| _                            | 16µs / channel in sequencer mode                           |  |  |

| Accuracy                     | ±2 LSB @ 25°C after calibration                            |  |  |

| Linearity                    | ±2 LSB @ 25°C after calibration                            |  |  |

| ADC INL/DNL Error            | ±3 LSB                                                     |  |  |

| Analog Output                |                                                            |  |  |

| Number of Analog Outputs     | 8 analog output channels                                   |  |  |

| Output Voltage Range         | ±10V                                                       |  |  |

| Calibration Data             | Calibration data for gain and offset correction in ID PROM |  |  |

| Resolution                   | 16 bit                                                     |  |  |

| Conversion Time              | 10μs max.                                                  |  |  |

| Accuracy                     | ±1 LSB @ 25°C after calibration                            |  |  |

| Linearity                    | ±2 LSB @ 25°C after calibration                            |  |  |

| DAC INL/DNL Error            | ±4/±3 LSB                                                  |  |  |

| Capacitive Load              | Up to 10 000pF                                             |  |  |

| Digital I/O            | Digital I/O                                                                                                                                                                                                                                                                                                                                                 |                                                                                 |  |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

| Number of Digital I/O  | 16 digital I/O d                                                                                                                                                                                                                                                                                                                                            | 16 digital I/O channels                                                         |  |  |  |  |

| Overvoltage Protection | 30V                                                                                                                                                                                                                                                                                                                                                         | 30V                                                                             |  |  |  |  |

| Minimum Pulse Width    | Programmable                                                                                                                                                                                                                                                                                                                                                | e, 100ns – 6.55ms                                                               |  |  |  |  |

| I/O Interface          |                                                                                                                                                                                                                                                                                                                                                             |                                                                                 |  |  |  |  |

| I/O Connector          | Front I/O: HD6<br>No PMC P14 I                                                                                                                                                                                                                                                                                                                              | 58 SCSI-3 type female connector (AMP 787082-7)<br>I/O                           |  |  |  |  |

| Physical Data          |                                                                                                                                                                                                                                                                                                                                                             |                                                                                 |  |  |  |  |

| Power Requirements     | 165 mA typica                                                                                                                                                                                                                                                                                                                                               | 295 mA typical @ +3.3V DC<br>165 mA typical @ +5V DC<br>10 mA typical @ -12V DC |  |  |  |  |

| Temperature Range      | Operating -40°C to +85 °C<br>Storage -40°C to +85°C                                                                                                                                                                                                                                                                                                         |                                                                                 |  |  |  |  |

| MTBF                   | 330000 h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation. |                                                                                 |  |  |  |  |

| Humidity               | 5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                     |                                                                                 |  |  |  |  |

| Weight                 | 82 g                                                                                                                                                                                                                                                                                                                                                        |                                                                                 |  |  |  |  |

Table 2-1: Technical Specification

# 3 Local Space Addressing

## 3.1 PCI9030 Local Space Configuration

The local on board addressable regions are accessed from the PCI side by using the PCI9030 local spaces.

| PCI9030<br>Local<br>Space | PCI9030 PCI Base Address (Offset in PCI Configuration Space) | PCI Space<br>Mapping | Size<br>(Byte) | Port<br>Width<br>(Bit) | Endian<br>Mode | Description                     |

|---------------------------|--------------------------------------------------------------|----------------------|----------------|------------------------|----------------|---------------------------------|

| 0                         | 2 (0x18)                                                     | MEM                  | 512            | 32                     | BIG            | Local Register Address<br>Space |

| 1                         | 3 (0x1C)                                                     | MEM                  | 64             | 16                     | BIG            | Sequencer Data RAM              |

| 2                         | 4 (0x20)                                                     | MEM                  | 64             | 16                     | BIG            | ADC/DAC Calibration<br>ROM Data |

| 3                         | 5 (0x24)                                                     | -                    | -              | -                      | -              | Not Used                        |

Table 3-1: PCI9030 Local Space Configuration

# 3.2 Local Register Address Space

PCI Base Address: PCI9030 PCI Base Address 2 (Offset 0x18 in PCI Configuration Space).

The register offsets stated below refer to 32 bit accesses. The registers shorter than 32 bit are filled with zeros on long word read-accesses. Refer to chapter 'Big/Little Endian' or the following table for correct word- or byte-wide accesses.

| Access Width | Register Bits      |                       |                       |                       |  |

|--------------|--------------------|-----------------------|-----------------------|-----------------------|--|

|              | [31:24]            | [23:16]               | [15:8]                | [7:0]                 |  |

| 32 bit       | Register Offset    |                       |                       |                       |  |

| 16 bit       | Registe            | r Offset              | Register              | Offset +2             |  |

| 8 bit        | Register<br>Offset | Register<br>Offset +1 | Register<br>Offset +2 | Register<br>Offset +3 |  |

Table 3-2: Register word/byte Accesses

| Offset to PCI Base<br>Address 2 | Symbol     | Register Name                      |

|---------------------------------|------------|------------------------------------|

| 0x0000                          | ADCCONT    | ADC Control Register               |

| 0x0004                          | ADCDATA    | ADC Data Register                  |

| 0x0008                          | ADCSTAT    | ADC Status Register                |

| 0x000C                          | ADCCONV    | ADC Conversion Start Register      |

| 0x0010                          | ADCSEQCONT | ADC Sequencer Control Register     |

| 0x0014                          | ADCSEQSTAT | ADC Sequencer Status Register      |

| 0x0018                          | ADCSEQTIME | ADC Sequencer Timer Register       |

| 0x001C                          | -          | Not used                           |

| 0x0020 - 0x009C                 | ADCSEQIRAM | ADC Sequencer Instruction RAM 1-32 |

| 0x00A0 - 0x00BF                 | -          | Not used                           |

| Offset to PCI Base<br>Address 2 | Symbol     | Register Name                   |

|---------------------------------|------------|---------------------------------|

| 0x00C0                          | DACCONT    | DAC Control Register            |

| 0x00C4                          | DACSEQSTAT | DAC Sequencer Status Register   |

| 0x00C8                          | DACSEQTIME | DAC Sequencer Timer Register    |

| 0x00CC                          | -          | Not used                        |

| 0x00D0 - 0x00EC                 | DACDATA    | DAC Data Register 1-8           |

| 0x00F0 - 0x00FF                 | -          | Not used                        |

| 0x0100                          | LINEDIR    | Line Direction Register         |

| 0x0104                          | LINEDEB    | Line Debounce Enable Register   |

| 0x0108                          | LINEDBT    | Line Debounce Time Register     |

| 0x010C                          | LINEIN     | Line Input Register             |

| 0x0110                          | LINEOUT    | Line Output Register            |

| 0x0114                          | LINEIEN    | Line Interrupt Enable Register  |

| 0x0118                          | LINEIST    | Line Interrupt Status Register  |

| 0x011C                          | -          | Not used                        |

| 0x0120                          | CNTPRL     | Counter Preload Register        |

| 0x0124                          | CNTCMP     | Counter Compare Register        |

| 0x0128                          | CNTDATA    | Counter Data Register           |

| 0x012C                          | CNTCONT    | Counter Control Register        |

| 0x0130                          | CNTSTAT    | Counter Status Register         |

| 0x0134                          | CNTCOM     | Counter Command Register        |

| 0x0138 – 0x013F                 | -          | Not used                        |

| 0x0140                          | ICR        | Interrupt Control Register      |

| 0x0144 - 0x014F                 | -          | Factory use only. Do not Write. |

| 0x0150 - 0x01FF                 | -          | Not used                        |

Table 3-3: Register Address Space

Addresses "Not used" will return 0 when read.

## 3.2.1 Analog Input Registers

## 3.2.1.1 ADC Control Register ADCCONT (Offset 0x0000)

| Bit   | Symbol     | Description                                                                                                                                                        | l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                 |                                                 | Access | Reset<br>Value |

|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------|--------|----------------|

| 31:12 | -          | Reserved Write: don't care Read: always reads as '0'                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                                 |        | 0              |

| 11    | RST        |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NDC is reset. Curre                                             | nt conversions are aborted.                     | R/W    | 0              |

| 10    | IRQC       | (ADC_BUS)                                                                                                                                                          | r Conversion Conversion will be general changes from the contraction of the conversion of the conversi | n disabled<br>n enabled<br>erated after a conve<br>rom 1 to 0). | ersion is finished<br>wledge see the ADC Status | R/W    | 0              |

| 9     | IRQST      | 0 = IRQ afte<br>1 = IRQ afte<br>An interrupt<br>(SETTL_BU                                                                                                          | IRQ after Settling Time Enable 0 = IRQ after Settling Time disabled 1 = IRQ after Settling Time enabled An interrupt will be generated after the settling time has elapsed (SETTL_BUSY changes from 1 to 0) For pending interrupts and interrupt acknowledge see the ADC Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                                 |        |                |

| 8     | ASTC       | 0 = OFF (No<br>A conversion<br>Register AD<br>1 = ON (Aut                                                                                                          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                 |                                                 |        |                |

| 7:6   | GAIN [1:0] | Gain Selecti GAIN1 0 0 1                                                                                                                                           | on (Analog GAIN0 0 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Gain Factor  1  2  4  8                                         | Input Voltage Range ±10V ±5V ±2.5V ±1.25V       | R/W    | 00             |

| 5     | SE/DIFF    | Single/Differential Mode Control  0 = Single-ended mode  32 single-ended input channels available  1 = Differential mode  16 differential input channels available |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                                 | R/W    | 0              |

| Bit | Symbol  | Description                           |                                        |                                     | Access | Reset<br>Value |

|-----|---------|---------------------------------------|----------------------------------------|-------------------------------------|--------|----------------|

| 4:0 | CS[4:0] | Channel Select (Analog Input Channel) |                                        |                                     | R/W    | 00000          |

|     |         | CS[4:0]                               | Single-ended<br>Channel<br>SE/DIFF = 0 | Differential Channel<br>SE/DIFF = 1 |        |                |

|     |         | 00000                                 | CH1                                    | CH1                                 |        |                |

|     |         |                                       |                                        |                                     |        |                |

|     |         | 01111                                 | CH16                                   | CH16                                |        |                |

|     |         | 10000                                 | CH17                                   | N/A                                 |        |                |

|     |         |                                       |                                        |                                     |        |                |

|     |         | 11111                                 | CH32                                   | N/A                                 |        |                |

|     |         | 'N/A' = ADC Input conn                | ected to GND                           |                                     |        |                |

Table 3-4: ADC Control Register

A write to this register sets the new channel and gain. Subsequent write accesses are ignored until the settling time has elapsed. This register is developed for a word (16 bit) or long word (32 bit) read/write access. Byte accesses on this register are not supported and will fail.

Do NOT write to this register while the sequencer is running! A write to this register while the sequencer is running can lead to unpredictable results!

Interrupts are generated only if the Master Interrupt Enable (MIE) is enabled in the Interrupt Control Register ICR.

#### 3.2.1.2 ADC Data Register ADCDATA (Offset 0x0004)

The ADC Data Register contains the converted data value. The output format is two's complement.

This register is updated if the conversion was initiated with the ADC Conversion Start Register ADCCONV or by the Automatic Settling Time Control ASTC on the falling edge of ADC\_BUSY in the ADC Status Register (ADCSTAT). Conversions initiated by the sequencer will have no effect to this register.

| Bit   | Symbol | Description                             | Access | Reset<br>Value |

|-------|--------|-----------------------------------------|--------|----------------|

| 31:16 | -      | Reserved Write: don't care              | R      | 0              |

|       |        | Read: always reads as '0'               |        |                |

| 15:0  |        | Stores the converted 16 bit data value. | R      | 0              |

Table 3-5 : ADC Data Register

| Description              | ±10V<br>(Gain 1) | ±5V (Gain 2) | ±2.5V<br>(Gain 4) | ±1.25V<br>(Gain 8) | Two's<br>Complement |

|--------------------------|------------------|--------------|-------------------|--------------------|---------------------|

| Full Scale Range         | ±10V             | ±5V          | ±2.5              | ±1.25              |                     |

| Least Significant<br>Bit | 305.2µV          | 152.6µV      | 76.2µV            | 38.15µV            |                     |

| FSR - 1LSB               | 9.999695V        | 4.999847V    | 2.499924V         | 1.249962V          | 0x7FFF¹             |

| Midscale + 1LSB          | 305.2µV          | 152.6µV      | 76.2µV            | 38.15µV            | 0x0001              |

| Midscale                 | 0V               | 0V           | 0V                | 0V                 | 0x0000              |

| Midscale – 1LSB          | -305.2µV         | -152.6µV     | -76.2µV           | -38.15µV           | 0xFFFF              |

| -FSR + 1LSB              | -9.999695V       | -4.999847V   | -2.499924V        | -1.249962V         |                     |

| Full Scale (neg.)        | -10V             | -5V          | -2.5V             | 1.25V              | 0x8000²             |

<sup>&</sup>lt;sup>1</sup>This is also the code for an overrange analog input.

Table 3-6: ADC Data Coding

After power up the on board ADC device is in a random state and requires two dummy conversions before operating correctly. This is based on the chip design of the ADC device.

Software should ignore the data of the first two ADC conversions after power-up.

The software drivers from TEWS TECHNOLOGIES already include these two dummy conversions.

<sup>&</sup>lt;sup>2</sup>This is also the code for an underrange analog input.

## 3.2.1.3 ADC Status Register ADCSTAT (Offset 0x0008)

| Bit  | Symbol        | Description                                                                                                                                                                                                                                                                                                                                                                               | Access | Reset<br>Value |

|------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:4 | -             | Reserved Write: don't care                                                                                                                                                                                                                                                                                                                                                                | R      | 0              |

| 3    | SETTL<br>IRQ  | Read: always read as '0'  Pending Settling Time Interrupts (Read), Interrupt acknowledge (Write)  On a read-access this bit shows a pending Settling Time interrupt. Pending interrupts are marked with a '1'.  An interrupt is acknowledged by writing a '1' to this bit after the error flags are cleared.                                                                              | R/C    | 0              |

| 2    | ADC IRQ       | Pending Conversion Interrupts (Read), Interrupt acknowledge (Write) On a read-access this bit shows a pending Conversion interrupt. Pending interrupts are marked with a '1'. An interrupt is acknowledged by writing a '1' to this bit after the error flags are cleared.                                                                                                                | R/C    | 0              |

| 1    | SETTL<br>BUSY | SETTL_BUSY Indicates that the required settling time after a write to the CONTREG register is not yet done. This bit is set by writing to the CONTREG register. The bit is cleared when the required settling time has elapsed. This bit must be read as '0' before a conversion is started by a write to the ADC Conversion Start Register ADCCONV. The ADC settling time is appr. 16µs. | R      | 0              |

| 0    | ADC<br>BUSY   | ADC_BUSY Indicates if an actual data conversion is in progress. If "Automatic Settling Time Mode" is OFF, this bit is set by writing to the ADC Conversion Start Register ADCCONV. If "Automatic Settling Time Mode" is ON, this bit is set automatically after the settling time has elapsed. This bit must be read as '0' before the conversion data is read from the DATAREG register. | R      | 0              |

Table 3-7: ADC Status Register

Interrupts are generated only if the Master Interrupt Enable (MIE) is enabled in the Interrupt Control Register ICR.

#### 3.2.1.4 ADC Conversion Start Register ADCCONV (Offset 0x000C)

The ADC Conversion Start Register is used to start an ADC conversion when "Automatic Settling Time Mode" is OFF. Any write access starts the conversion. The user must read the SETTL\_BUSY bit in the ADC Status Register as '0' or wait for a Settling Time Interrupt before the conversion is started. The ADC\_BUSY bit in the ADC Status Register indicates if the conversion data in the ADC Data Register is valid (ADC\_BUSY bit = '0').

It is allowed to set up a new channel/gain by writing to the ADC Control Register CONTREG immediately after starting an ADC conversion.

If "Sequencer Mode" is selected (SEQCONT register bit 0 is set to '1') all write accesses to the ADC Conversion Start Register ADCCONV are ignored.

Please pay attention to the chapter "Important Notes".

#### 3.2.1.5 ADC Sequencer Control Register ADCSEQCONT (Offset 0x0010)

| Bit  | Symbol  | Description                                                                                                                           | Access | Reset<br>Value |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:3 | -       | Reserved                                                                                                                              | R      | 0              |

|      |         | Write: don't care                                                                                                                     |        |                |

|      |         | Read: always reads as '0'                                                                                                             |        |                |

| 2    | SEQ INT | Sequencer Interrupt Enable Control                                                                                                    | R/W    | 0              |

|      | ENA     | 0 = Sequencer Interrupt Disabled                                                                                                      |        |                |

|      |         | 1 = Sequencer Interrupt Enabled                                                                                                       |        |                |

|      |         | An interrupt request will be generated if any error flag is set in the ADCSEQSTAT Register (Sequencer Data Valid or Sequencer Error). |        |                |

|      |         | For pending interrupts and interrupt acknowledge see ADC Sequencer Status Register ADCSEQSTAT.                                        |        |                |

| 1    | SEQ     | Sequencer Trigger Source                                                                                                              | R/W    | 0              |

|      | TRIG    | 0 = Sequencer Timer                                                                                                                   |        |                |

|      |         | 1 = External Signal (Dig I/O Line 0)                                                                                                  |        |                |

| 0    | SEQ ON  | Sequencer Start / Stop Control                                                                                                        | R/W    | 0              |

|      |         | 0 = Stops the Sequencer after last Instruction (Sequencer Continuous Mode: Sequencer stops immediately). No DATA AV will be issued.   |        |                |

|      |         | 1 = Starts the Sequencer immediately                                                                                                  |        |                |

Table 3-8: ADC Sequencer Control Register

If an error flag (DATA\_OVERFLOW\_ERROR, TIMER\_ERROR, I-RAM\_ERROR) is set in the Sequencer Status Register SEQSTAT, the sequencer will be stopped after the last instruction (SEQ\_ON will be set to '0'). The user must clear the status bits and start the sequencer again.

Interrupts are generated only if the Master Interrupt Enable (MIE) is enabled in the Interrupt Control Register ICR.

Please pay attention to the chapter "Important Notes" before using the sequencer.

If ADC\_OUT in the Line Direction Register LINEDIR is set to '1', the trigger signal for the sequencer is available for external use on Dig I/O Line 0.

Do not use the External Signal as Sequencer Trigger Source if ADC\_OUT is enabled. This will cause the sequencer to lock.

## 3.2.1.6 ADC Sequencer Status Register ADCSEQSTAT (Offset 0x0014)

| Bit  | Symbol                    | Description                                                                                                                                                                                                                                                                                                                                                          | Access | Reset<br>Value |

|------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:5 | -                         | Reserved Write: don't care Read: always reads as '0'                                                                                                                                                                                                                                                                                                                 | R      | 0              |

| 4    | SEQ IRQ                   | Pending Sequencer Interrupts (Read), On a read-access this bit shows a pending Sequencer interrupt. Pending interrupts are marked with a '1'. An interrupt is acknowledged when the error flags are cleared.                                                                                                                                                         | R      | 0              |

| 3    | I-RAM<br>ERROR            | Instruction RAM Error Flag Set by the sequencer if the sequencer has been started and there is no instruction in the Sequencer Instruction RAM. To clear this flag the user must write '1' to this bit.                                                                                                                                                              | R/C    | 0              |

| 2    | TIMER<br>ERROR            | Timer Error Flag Set by the sequencer if the sequencer timer has elapsed but the actual sequence is still in progress. To clear the Timer Error Flag the user must write '1' to this bit. If the Sequencer Timer Register is 0 (Sequencer Continuous Mode) the Timer Error Flag always reads as '0'.                                                                 | R/C    | 0              |

| 1    | DATA<br>OVERFLOW<br>ERROR | Data Overflow Error Flag Set by the sequencer if the last sequencer instruction is done and the Data Available Flag of the previous sequence has not yet been cleared by the user.  To clear the error flag the user must write '1' to this bit.  If the Sequencer Timer Register is 0 (Sequencer Continuous Mode) the Data Overflow Error Flag always reads as '0'. | R/C    | 0              |

| 0    | DATA AV                   | Data Available Flag Set if a sequence is done and new ADC Data is available in the ADC Data RAM. After reading the ADC Data RAM the user must clear the Data Available Flag by writing '1' to this bit.                                                                                                                                                              | R/C    | 0              |

Table 3-9: ADC Sequencer Status Register

| Description                | Sequencer<br>Timer | Continuous<br>Mode | External<br>Trigger |

|----------------------------|--------------------|--------------------|---------------------|

| Data Available Flag        | Active, IRQ        | Active, no IRQ     | Active, IRQ         |

| Data Overflow Error Flag   | Active, IRQ        | Disabled           | Active, IRQ         |

| Timer Error Flag           | Active, IRQ        | Disabled           | Active, IRQ         |

| Instruction RAM Error Flag | Active, IRQ        | Active, IRQ        | Active, IRQ         |

Table 3-10: Error Flag IRQ generation

Also see chapter 'Sequencer Errors' for details.

#### 3.2.1.7 ADC Sequencer Timer Register ADCSEQTIME (Offset 0x0018)

| Bit   | Symbol | Description                                          | Access | Reset<br>Value |

|-------|--------|------------------------------------------------------|--------|----------------|

| 31:16 | -      | Reserved Write: don't care Read: always reads as '0' | R      | 0              |

| 0:15  |        | Sequencer Timer Preload Value                        | R/W    | 0              |

Table 3-11: ADC Sequencer Timer Register

The Sequencer Timer is programmable from 100µs to 6.5535s in 100µs steps. The time base for the sequencer timer is derived from an on board 40 MHz oscillator.

Whenever the timer reaches the programmed value the sequencer starts a new sequence with the first instruction found in the instruction RAM.

Assure that the time needed to complete a sequence is suitable to the chosen sequence timer value. If the sequence timer elapses while a sequence is still in progress, a timer error will be asserted.

If the Sequencer Timer Register is set to '0', the "Sequencer Continuous Mode" is selected. The sequencer will start again with the first instruction of the sequence immediately after the last instruction of the previous sequence has been completed. In this mode the Timer Error Flag (TIMER\_ERROR) and the Data Overflow Error Flag (DATA\_OVERFLOW\_ERROR) are not active and will read as '0'. The Data Available Flag (DATA\_AV) will be active, but will not produce an interrupt.

#### 3.2.1.8 ADC Sequencer Instruction RAM (Offset 0x0020 - Offset 0x009C)

| Bit  | Symbol  | Description                | Description                        |                                     |                                               |     | Reset<br>Value |

|------|---------|----------------------------|------------------------------------|-------------------------------------|-----------------------------------------------|-----|----------------|

| 31:4 | -       | Reserved                   |                                    |                                     |                                               |     | 0              |

|      |         | Write: don't<br>Read: alwa |                                    | יחי                                 |                                               |     |                |

| 3:2  | GAIN    |                            |                                    |                                     |                                               | DAM | 00             |

| 3:2  | [1:0]   |                            | ` ` `                              | g Input Amplifier)                  |                                               | R/W | 00             |

|      | [1.0]   | GAIN1                      | GAIN0                              | Gain Factor                         | Input Voltage Range                           |     |                |

|      |         | 0                          | 0                                  | 1                                   | ±10V                                          |     |                |

|      |         | 0                          | 1                                  | 2                                   | ±5V                                           |     |                |

|      |         | 1                          | 0                                  | 4                                   | ±2.5V                                         |     |                |

|      |         | 1                          | 1                                  | 8                                   | ±1.25V                                        |     |                |

|      |         |                            | •                                  |                                     | <u> </u>                                      |     |                |

| 1    | ENA     | Enable this                | ADC Chan                           | nel for the Seque                   | ncer                                          | R/W | 0              |

|      |         | 0 = Sequen                 | cer will pas                       | s over the ADC C                    | Channel                                       |     |                |

|      |         |                            |                                    | s this ADC Chan<br>RAM at the end o | nel and updates the ADC Data of the sequence. |     |                |

| 0    | SE/DIFF | Single/Diffe               | erential Mod                       | le Control                          |                                               | R/W | 0              |

|      |         | 0 = Single-e               | 0 = Single-ended mode              |                                     |                                               |     |                |

|      |         | 32 single e                | 32 single ended channels available |                                     |                                               |     |                |

|      |         | 1 = Differen               | 1 = Differential mode              |                                     |                                               |     |                |

|      |         | 16 different               | 6 differential channels available. |                                     |                                               |     |                |

|      |         |                            |                                    | n be configured a put for channels  | s differential channel. Channel<br>1 to 16.   | 5   |                |

Table 3-12: ADC Sequencer Instruction RAM Register