# XMC-CPU/Zulu

# XMC UltraScale+<sup>™</sup> Zynq<sup>®</sup> MPSoC Board with integrated FPGA

### Hardware Manual

to Product V.2031.01

#### **Notes**

The information in this document has been carefully checked and is believed to be entirely reliable. esd electronics makes no warranty of any kind with regard to the material in this document and assumes no responsibility for any errors that may appear in this document. In particular descriptions and technical data specified in this document may not be constituted to be guaranteed product features in any legal sense.

esd electronics reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance, or design.

All rights to this documentation are reserved by esd electronics. Distribution to third parties, and reproduction of this document in any form, whole or in part, are subject to esd electronics' written approval.

© 2022 esd electronics gmbh, Hannover

### esd electronics gmbh

Vahrenwalder Str. 207 30165 Hannover Germany

Tel.: +49-511-37298-0 Fax: +49-511-37298-68

E-Mail: info@esd.eu Internet: www.esd.eu

This manual contains important information and instructions on safe and efficient handling of the XMC-CPU/Zulu. Carefully read this manual before commencing any work and follow the instructions.

The manual is a product component, please retain it for future use.

#### **Trademark Notices**

VITATM is a trademark of the VMEbus International Trade Association in the United States and other countries. PCI Express® is a registered trademark of PCI-SIG.

Linux® is the registered trademark of Linus Torvalds in the United States and/or other countries.

VxWorks® is a registered trademark of Wind River Systems, Inc.

Xilinx® and Zynq® are registered trademarks of Xilinx. UltraScale $^{TM}$  is trademark of Xilinx, Inc.

EtherCAT® is registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany.

All other trademarks, product names, company names or company logos used in this manual are reserved by their respective owners.

### **Document Information**

| Document file:        | I:\Texte\Doku\MANUALS\PMC-XMC\XMC-CPU-Zulu\XMC-CPU-Zulu_Hardware-Manual_en_11.docx |

|-----------------------|------------------------------------------------------------------------------------|

| Date of print:        | 2022-08-10                                                                         |

| Document-type number: | DOC0800                                                                            |

| PCB version.: | 1.3 |

|---------------|-----|

### **Document History**

The changes in the document listed below affect changes in the hardware as well as changes in the description of the facts, only.

| Rev. | Chapter | Changes versus previous version | Date       |

|------|---------|---------------------------------|------------|

| 1.0  | -       | First English manual            | 2021-03-09 |

| 1.1  |         | Technical Information added     | 2022-06-23 |

Technical details are subject to change without further notice.

### **Classification of Warning Messages and Safety Instructions**

This manual contains noticeable descriptions, warning messages and safety instructions, which you must follow to avoid personal injuries or death and property damage.

This is the safety alert symbol.

It is used to alert you to potential personal injury hazards. Obey all safety messages and instructions that follow this symbol to avoid possible injury or death.

#### DANGER, WARNING, CAUTION

Depending on the hazard level the signal words DANGER, WARNING or CAUTION are used to highlight safety instructions and warning messages. These messages may also include a warning relating to property damage.

#### DANGER

Danger statements indicate a hazardous situation which, if not avoided, will result in death or serious injury.

#### WARNING.

Warning statements indicate a hazardous situation that, if not avoided, could result in death or serious injury.

#### CAUTION

Caution statements indicate a hazardous situation that, if not avoided, could result in minor or moderate injury.

### NOTICE

Notice statements are used to notify people on hazards that could result in things other than personal injury, like property damage.

### **NOTICE**

This NOTICE statement indicates that the device contains components sensitive to electrostatic discharge.

### NOTICE

This NOTICE statement contains the general mandatory sign and gives information that must be heeded and complied with for a safe use.

#### INFORMATION

#### INFORMATION

Notes to point out something important or useful.

# **Safety Instructions**

- •When working with the XMC-CPU/Zulu follow the instructions below and read the manual carefully to protect yourself from injury and the XMC-CPU/Zulu from damage.

- •The device is a built-in component. It is essential to ensure that the device is mounted in a way that cannot lead to endangering or injury of persons or damage to objects.

- Do not use damaged or defective cables to connect the XMC-CPU/Zulu ".

- •In case of damages to the device, which might affect safety, appropriate and immediate measures must be taken, that exclude an endangerment of persons and domestic animals and property.

- Current circuits which are connected to the device have to be sufficiently protected against hazardous voltage (SELV according to EN 60950-1).

- •The XMC-CPU/Zulu may only be driven by power supply current circuits, that are contact protected. A power supply, that provides a safety extra-low voltage (SELV) according to EN 60950-1, complies with these conditions.

- •The device has to be securely installed in the control cabinet before commissioning.

- Protect the XMC-CPU/Zulu from dust, moisture and steam.

- Protect the XMC-CPU/Zulu from shocks and vibrations.

- •The XMC-CPU/Zulu may become warm during normal use. Always allow adequate ventilation around the XMC-CPU/Zulu and use care when handling.

- Do not operate the XMC-CPU/Zulu adjacent to heat sources and do not expose it to unnecessary thermal radiation. Ensure an ambient temperature as specified in the technical data.

#### **DANGER**

Hazardous Voltage - Risk of electric shock due to unintentional contact with uninsulated live parts with high voltages inside of the system into which the XMC-CPU/Zulu is to be integrated.

- → All current circuits which are connected to the device have to be sufficiently protected against hazardous voltage (SELV according to EN 60950-1) before you start with the installation.

- → Ensure the absence of voltage before starting any electrical work

### **NOTICE**

#### Electrostatic discharges may cause damage to electronic components.

- → To avoid this, discharge the static electricity from your body before you touch the XMC-CPU/Zulu.

- Furthermore, you should prevent your clothes from touching the XMC-CPU/Zulu, because your clothes might be electrostatically charged as well.

#### **Qualified Personnel**

This documentation is directed exclusively towards personnel qualified in control and automation engineering. The installation and commissioning of the product may only be carried out by qualified personnel, which is authorized to put devices, systems, and electric circuits into operation according to the applicable national standards of safety engineering.

### Conformity

The XMC-CPU/Zulu is an industrial product and meets the demands of the EU regulations and EMC standards printed in the conformity declaration at the end of this manual.

**Warning:** In a residential, commercial or light industrial environment the XMC-CPU/Zulu may cause radio interferences in which case the user may be required to take adequate measures.

The XMC-CPU/Zulu is a sub-assembly intended for incorporation into an. The manufacturer of the final system must decide whether additional EMC or EMI protection requirements are necessary.

### **Data Safety**

This device is equipped with an Ethernet or other interface which is suitable to establish a connection to data networks. Depending on the software used on the device, these interfaces may allow attackers to compromise normal function, get illegal access or cause damage.

esd does not take responsibility for any damage caused by the device if operated at any networks. It is the responsibility of the device's user to take care that necessary safety precautions for the device's network interface are in place.

#### **Intended Use**

The intended use of the XMC-CPU/Zulu is the operation as XMC Zynq MPSoC device with FPGA. The guarantee given by esd does not cover damages which result from improper use, usage not in accordance with regulations or disregard of safety instructions and warnings.

- The XMC-CPU/Zulu is intended for installation on a base board according to Vita 42.3 standard.

- The operation of the XMC-CPU/Zulu in hazardous areas, or areas exposed to potentially explosive materials is not permitted.

- The operation of the XMC-CPU/Zulu for medical purposes is prohibited.

#### **Service Note**

The XMC-CPU/Zulu does not contain any parts that require maintenance by the user. The XMC-CPU/Zulu does not require any manual configuration of the hardware. Unauthorized intervention in the device voids warranty claims

### **Disposal**

Products marked with a crossed-out dustbin must not be disposed of with household waste. Devices which have become defective in the long run must be disposed in an appropriate way or must be returned to the manufacturer for proper disposal. Please, contribute to environmental protection.

### **Typographical Conventions**

Throughout this manual the following typographical conventions are used to distinguish technical terms.

| Convention             | Example                          |

|------------------------|----------------------------------|

| File and path names    | /dev/null Or <stdio.h></stdio.h> |

| Function names         | open()                           |

| Programming constants  | NULL                             |

| Programming data types | uint32_t                         |

| Variable names         | Count                            |

#### **Number Representation**

All numbers in this document are base 10 unless designated otherwise. Hexadecimal numbers have a prefix of 0x, and binary numbers have a prefix of 0b. For example, 42 is represented as 0x2A in hexadecimal and 0b101010 in binary.

### **Table of Contents**

|   |                 | nstructions                                  |      |

|---|-----------------|----------------------------------------------|------|

| 1 | Over            | rview                                        | 9    |

|   | 1.1             | Description of XMC-CPU/Zulu                  | g    |

|   | 1.2             | Glossary                                     |      |

| 2 |                 | View with Connectors                         |      |

|   |                 | S                                            |      |

| J |                 | Position of the LEDs                         |      |

|   | J. I            | 3.1.1 Position                               |      |

|   |                 |                                              |      |

|   |                 | 3.1.2 Indication of Ethernet LEDs ETH0, ETH1 |      |

|   |                 | 3.1.3 Indication of the Tricolour LEDs 0-4   |      |

|   | 3.2             | LEDs on PCB                                  |      |

|   |                 | 3.2.1 Ethernet LEDs                          |      |

|   |                 | 3.2.2 Other LEDs                             |      |

| 4 | Hard            | lware Configuration                          | . 17 |

|   | 4.1             | Coding Switch and Reset Buttons              | . 17 |

|   |                 | 4.1.1 Mode                                   |      |

|   |                 | 4.1.2 PROG, SRST, POR                        | . 18 |

| 5 | Hard            | Iware Installation                           |      |

|   |                 | nnical Data                                  |      |

| U | 6.1             | General Technical Data                       |      |

|   | -               | CPU Kernel                                   |      |

|   |                 |                                              |      |

|   |                 | Ethernet Interface PS                        |      |

|   | 6.4             | Ethernet Interface PL                        |      |

|   |                 | USB Console Port (CON)                       |      |

|   | 6.6             | PCIe Interfaces                              |      |

|   | 6.7             | Digital Inputs/Outputs P4                    |      |

|   | 6.8             | Digital Inputs/Outputs P6                    | . 25 |

|   | 6.9             | Control Elements                             | . 26 |

|   | 6.10            | Health                                       | . 26 |

|   |                 | Mass Storage                                 |      |

|   |                 | MicroSD Card Slot                            |      |

|   |                 | Front Panel LEDs.                            |      |

|   |                 | PCI Clock Generator                          |      |

|   |                 |                                              |      |

|   | 0.15            | Optional Interfaces                          |      |

|   |                 | 6.15.1 CAN Interfaces                        | _    |

| _ | _               | 6.15.2 PMC Interface                         |      |

| 7 |                 | nector Assignments                           |      |

|   | 7.1             | PMC/XMC Connectors                           |      |

|   |                 | 7.1.1 PMC P1 Connector                       |      |

|   |                 | 7.1.2 PMC P2 Connector                       |      |

|   |                 | 7.1.3 PMC P4 I/O Connector                   | . 31 |

|   |                 | 7.1.4 XMC - P5                               | . 33 |

|   |                 | 7.1.5 XMC – P6 I/O Connector                 |      |

|   | 7.2             | Ethernet ETH0, ETH1                          |      |

|   |                 | USB Console Port – CON (X1220)               |      |

|   |                 | Adapters                                     |      |

|   | / . <del></del> | 7.4.1 XMC-CPU-ADAPTER-FPGA                   |      |

|   |                 |                                              |      |

| 0 | 0.4             | 7.4.2 XMC-JTAG-Adapter                       |      |

| ŏ |                 | ware                                         |      |

|   | 8.1             | Introduction                                 |      |

|   |                 | Overview of Software Components              |      |

|   | 8.3             | Licenses                                     |      |

|   |                 | 8.3.1 Bootloader                             |      |

|   |                 | 8.3.2 Operating System                       | . 41 |

|              | 8.3.3 VHDL-Code                                       |     |

|--------------|-------------------------------------------------------|-----|

| 8.4          | Generating Firmware Image                             | 42  |

| 8.5          | Software                                              | 43  |

|              | 8.5.1 Peta Linux                                      | 43  |

|              | 8.5.2 U-Boot                                          | -   |

|              | 8.5.3 Linux                                           |     |

|              |                                                       |     |

|              | 8.5.4 VHDL-Code                                       |     |

|              | ferences                                              |     |

|              | claration of Conformity                               |     |

| 11 Ord       | der Information                                       | 46  |

| 11.          | 1 Hardware                                            | 46  |

| 11.          | 2 Manuals                                             | 46  |

|              |                                                       |     |

|              |                                                       |     |

| List         | of Tables                                             |     |

| Table        | 1: Description of LEDs                                | 1.1 |

|              |                                                       |     |

|              | 2: Description of LEDs 0-4                            |     |

|              | 3: Ethernet LEDs on the PCB                           |     |

|              | 4: LEDs CON, Activity and USB PWR                     |     |

|              | 5: MODE switch                                        |     |

| <b>Table</b> | 6: MODE switch configuration                          | 17  |

| <b>Table</b> | 7: Reset signals                                      | 18  |

|              | 8: General Data of the module                         |     |

|              | 9: CPU Kernel                                         |     |

|              | 10: Data of the Ethernet interface PS                 |     |

|              | 11: Data of the Ethernet interface PL                 |     |

|              |                                                       |     |

|              | 12: Data of the USB console port                      |     |

|              | 13: Data of the PCIe interface                        |     |

|              | 14: Data of the Digital I/Os on P4                    |     |

| Table        | 15: Data of the Digital I/Os on P6                    | 25  |

| <b>Table</b> | 16: Data of the control elements and display elements | 26  |

|              | 17: Health unit                                       |     |

|              | 18: Data of the mass storage unit                     |     |

|              | 19: Data of the MicroSD card slot                     |     |

|              |                                                       |     |

|              | 20: Front panel LEDs                                  |     |

| lable        | 21: PCI Clock generator                               | 27  |

|              | 22: Data of the optional CAN interfaces               |     |

|              | 23: Data of the optional PMC interface                |     |

| <b>Table</b> | 24: Order information for XMC-CPU/Zulu                | 46  |

|              | 25: Available Manuals                                 |     |

|              |                                                       |     |

| List         | of Figures                                            |     |

|              | •                                                     | _   |

|              | e 1: Block circuit diagram                            |     |

|              | e 2: PCB top view                                     |     |

| Figure       | e 3: PCB bottom view                                  | 12  |

|              | e 4: Connectors and LEDs                              |     |

|              | e 5: Connectors and LEDs                              |     |

|              | e 6: Position of the switches (detail)                |     |

|              | e 7: XMC-CPU-ADAPTER-FPGA                             |     |

| _            |                                                       |     |

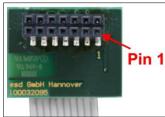

| _            | e 8:Socket strip                                      |     |

| _            | e 9: Header                                           |     |

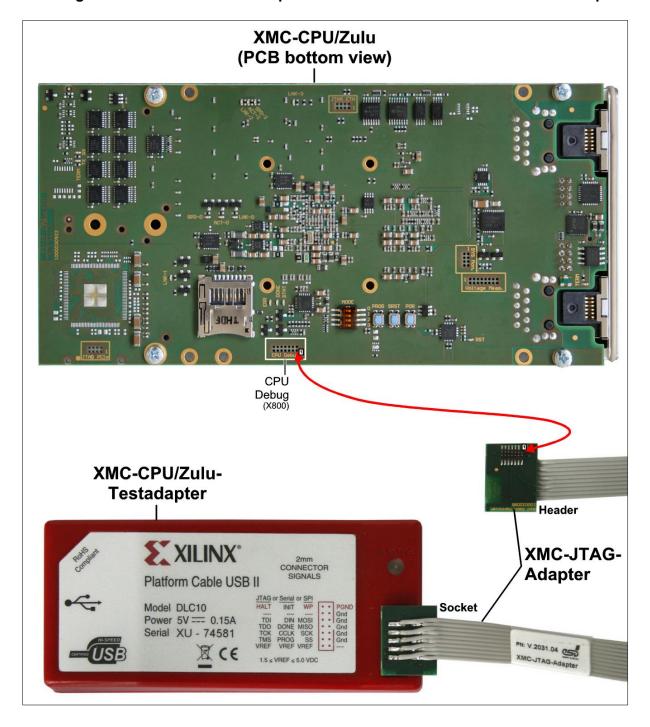

|              | e 10: XMC-JTAG-Adapter                                |     |

| Figure       | e 11: Connecting diagram of the XMC-JTAG-Adapter      | 39  |

### 1 Overview

### 1.1 Description of XMC-CPU/Zulu

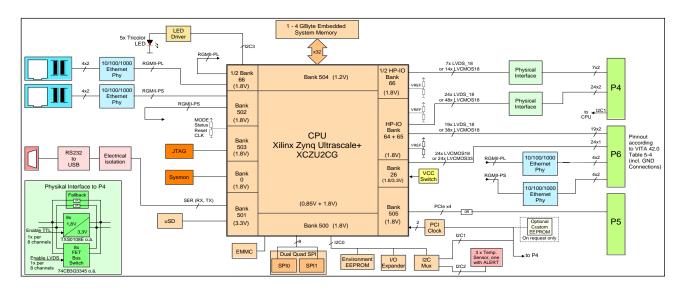

Figure 1: Block circuit diagram

#### 64-Bit XMC ARM® Host CPU

The XMC-CPU/Zulu in XMC form factor comes with a XILINX<sup>®</sup> Zynq<sup>®</sup> UltraScale+<sup>™</sup> CG multiprocessor system-on-chip with 1.3 GHz core frequency.

The local memory bus has a bus width of 32 bits and an overall capacity of 1 Gbyte.

64 Mbyte SPI Flash for boot loader and 128 Kbit I<sup>2</sup>C EEPROM for U-Boot environment.

XMC-CPU/Zulu features a 16-Gbyte eMMC<sup>™</sup> memory which is used for operating system, file system and application software.

The XMC interface comes with quad-lane PCIe<sup>®</sup> bus and is designed according to VITA<sup>™</sup> 42.3.

Two Gigabit Ethernet interfaces are accessible via the front panel of the XMC-CPU/Zulu. This gives an excellent base for EtherCAT® applications.

Two additional rear IO Ethernet interfaces are accessible via the XMC connector P6. The rear IO Ethernet interfaces come without electrical isolation.

Two of the GB Ethernet interfaces (one front, one rear) are routed through the FPGA. Therefore, special Ethernet IP-cores can be implemented.

A serial interface, designed as terminal interface, is accessible via an USB Mini type-B connector on the front.

The Flash memory carries the standard boot program "Das U-Boot" and enables the XMC-CPU/Zulu to boot various operating systems from on-board Flash, network or eMMC.

Board support packages are available for Linux® and VxWorks®. The BSPs include an example source code for the FPGA. Programming of the FPGA is done via XILINX Toolchain.

The esd EtherCAT Master Stack is available for various operating systems.

#### Overview

Customized options are available for customized series production in reasonable quantities. Please contact our sales team for detailed information. For example:

#### - CAN

esd offers standard PIM modules for CAN signals.

Furthermore, a CAN IP-core (CAN esdACC), which is configurable (number of CAN nodes, routing FPGA  $\leftrightarrow$  P4), is available for the on-board FPGA on request.

#### - IRIG-B

An IRIG-B IP Core by esd electronics can be implemented in the FPGA. The physical interface of IRIG-B has to be provided externally via a PIM module. An esd PIM module is available on request.

#### - Other CPU Types

Furthermore, other CPU-types (ZU2EG, ZU3CG and ZU3EG) are applicable.

#### - Extended Temperature Range

The temperature range can be extended to -40 °C up to 75 °C.

### - PMC

PMC according to IEEE Std. 1386-2001 instead of XMC interface via connectors P1 and P2. The PCI bus conforms to PCI Local Bus Specification 3.0, 32-bit 33/66 MHz, 3.3 V (5 V tolerant), PCI bus master capability. The PMC interface supports 32-bit / 66 MHz PCI bus according to PCI Local Bus Specification 3.0.

#### - Ethernet

The rear IO Ethernet signals are connected via P6. To connect standard Ethernet cabling an esd PIM module is available on request. The PIM module comes with an RJ45 connector and the Ethernet transformers on-board.

#### - RTC

An additional RTC can be equipped.

A backup battery can be connected via P4 and P6.

### - Software

Please contact our <u>Sales-Team</u> for board support packages for other real-time operating systems (e.g. QNX).

# 1.2 Glossary

### **Abbreviations**

| <b>Abbreviation</b> | Term                                                 |

|---------------------|------------------------------------------------------|

| API                 | Application Programming Interface                    |

| CAN                 | Controller Area Network                              |

| CPU                 | Central Processing Unit                              |

| CiA                 | CAN in Automation                                    |

| FPGA                | Field Programmable Gate Array                        |

| FSBL                | First Stage Bootloader                               |

| HW                  | Hardware                                             |

| I/O                 | Input/Output                                         |

| LSB                 | Least Significant Bit                                |

| MSB                 | Most Significant Bit                                 |

| n.a.                | not applicable                                       |

| OS                  | Operating System                                     |

| PS                  | Processing System (APUs + Memory + Ethernet etc.)    |

| PL                  | Programmable Logic (FPGA)                            |

| RTC                 | Real Time Clock                                      |

| SDK                 | Software Development Kit                             |

| VIVADO              | Xilinx development tool for the programming of FPGAs |

### 2 PCB View with Connectors

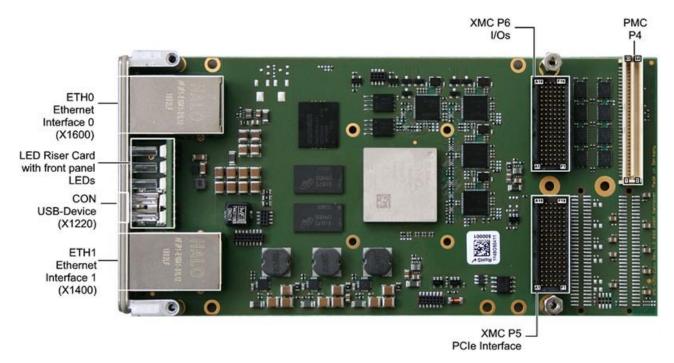

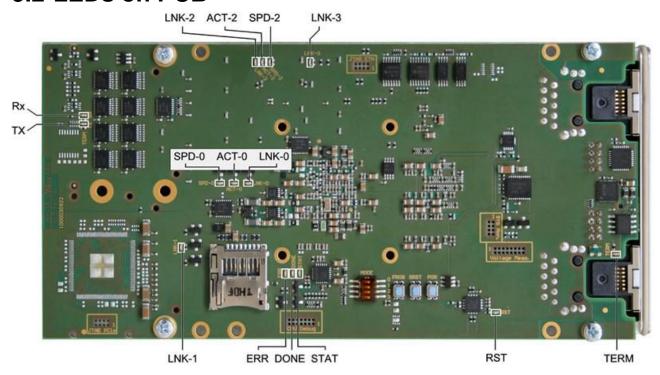

Figure 2: PCB top view

The Debug interface (X800) must be connected from the bottom side of the XMC-CPU/Zulu, see Figure 3.

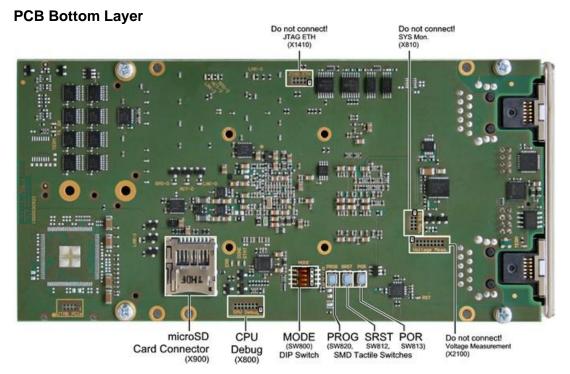

Figure 3: PCB bottom view

### **NOTICE**

Read chapter "Hardware Installation" on page 19, before you start with the installation of the hardware!

See also from page 29 for signal assignment of the CAN connectors. For a description of the DIP switch and the SMD tactile switches see page 17.

The LEDs are described in chapter "LEDs" page 14.

### 3 LEDs

### 3.1 Position of the LEDs

### 3.1.1 Position

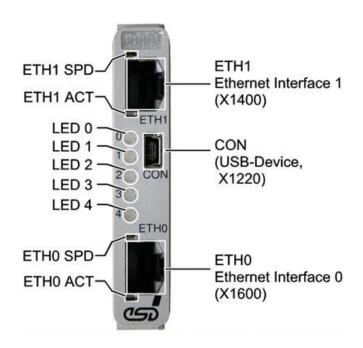

Figure 4: Connectors and LEDs

### 3.1.2 Indication of Ethernet LEDs ETH0, ETH1

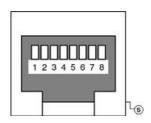

The Activity and Link/Speed LEDs are integrated in the RJ45 sockets of ETH0 and ETH1 and display the status of the corresponding ETH channel.

| LED | Colour | Function | Indicator<br>State | Description                                                     |

|-----|--------|----------|--------------------|-----------------------------------------------------------------|

| SPD | yellow | Speed    | ON                 | Ethernet bit rate: 1000 Mbit/s                                  |

| ACT | green  | Activity | flashing           | Ethernet activity (reception and transmission of Ethernet data) |

Table 1: Description of LEDs

### 3.1.3 Indication of the Tricolour LEDs 0-4

Five tricolour LEDs are equipped in the front panel.

| LED  | Colour | Description                                      |

|------|--------|--------------------------------------------------|

|      | green  |                                                  |

| LEDX | red    | User-defined via I <sup>2</sup> C bus and driver |

|      | blue   |                                                  |

(X = 0-4)

Table 2: Description of LEDs 0-4

### 3.2 LEDs on PCB

Figure 5: Connectors and LEDs

### 3.2.1 Ethernet LEDs

The 8 green LEDs (Speed, Activity and Link) are equipped on the bottom side of the XMC-CPU/Zulu see Figure 5.

| Zynq<br>Section                 | LED<br>Name<br>on PCB | Function | Display  | Meaning LED on                                                    | LED name<br>in schematic<br>diagram |

|---------------------------------|-----------------------|----------|----------|-------------------------------------------------------------------|-------------------------------------|

| PL-GEM                          | -                     | Speed    | -        | integrated in RJ45 socket in the front panel,                     | in X1600                            |

| (U600 M)<br>routed to           | -                     | Activity | -        | see chapter 3.1.2, page 14                                        | in X1600                            |

| PS-GEM0                         | LNK-3                 | Link     | on       | Ethernet link established                                         | LED1622                             |

| PL-GEM                          | SPD-2                 | Speed    | on       | Ethernet bit rate: 1000 Mbit/s                                    | LED1521                             |

| (U600L)<br>routed to<br>PS-GEM1 | ACT-2                 | Activity | flashing | Ethernet activity - (reception and transmission of Ethernet data) | LED1520                             |

| 1 0 OLIII1                      | LNK-2                 | Link     | on       | Ethernet link established                                         | LED1522                             |

|                                 | SPD-0                 | Speed    | on       | Ethernet bit rate: 1000 Mbit/s                                    | LED1321                             |

| <b>PS-GEM2</b> (U600H)          | ACT-0                 | Activity | flashing | Ethernet activity- (reception and transmission of Ethernet data)  | LED1320                             |

|                                 | LNK-0                 | Link     | on       | Ethernet link established                                         | LED1322                             |

| DO 05140                        | -                     | Speed    | -        | integrated in RJ45 socket in the front panel,                     | in X1400                            |

| <b>PS-GEM3</b> (U600F)          | -                     | Activity | -        | see chapter3.1.2, page 14                                         | in X1400                            |

|                                 | LNK-1                 | Link     | on       | Ethernet link established                                         | LED1422                             |

Table 3: Ethernet LEDs on the PCB

### 3.2.2 Other LEDs

The LEDs are equipped on the rear side of the XMC-CPU/Zulu, see Figure 5.

|                     | LED  | Colour | Function | Display  | Description (LED on)                                   | LED name in schematic diagram |

|---------------------|------|--------|----------|----------|--------------------------------------------------------|-------------------------------|

|                     | TX   | green  | SER0_Tx  | flashing | Transmitting data of serial interface via USB port CON | LED410                        |

| CON<br>port<br>LEDs | RX   | green  | SER0_RX  | flashing | Receiving data of serial interface via USB port CON    | LED411                        |

|                     | TERM | green  | Terminal | flashing | Traffic on serial interface via USB port CON (TERM)    | LED1222                       |

|                     | DONE | green  | Done     | on       | PL configuration done                                  | LED820                        |

| FPGA<br>LEDs        | ERR  | red    | Err Out  | on       | Accidental power loss, hardware error or PMU failure.  | LED821                        |

|                     | STAT | green  | ERR_Stat | on       | Platform Management Unit (PMU) dependent information   | LED822                        |

| System              | RST  | red    | Reset    | on       | Card reset active                                      | LED810                        |

Table 4: LEDs CON, Activity and USB PWR

# 4 Hardware Configuration

### 4.1 Coding Switch and Reset Buttons

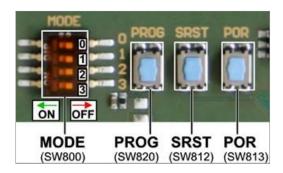

The DIP-switch MODE and the 3 SMD tactile switches PROG, SRST and POR are equipped on the bottom layer of the XMC-CPU/Zulu. See Figure 3 on page 12 for the position on the PCB.

Figure 6: Position of the switches (detail)

### 4.1.1 Mode

The DIP-switch MODE (PS\_MODE) comes with 4 Mode pins. With the DIP-switch the boot mode can be selected. Depending on the setting of the switches the BootROM boots the system from Quad-SPI (24b or 32b), SD or eMMC external boot devices.

| Coding<br>Switch | Pin |          | Description                                                                                                                |   |  |  |  |  |

|------------------|-----|----------|----------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

|                  | 0   | PS_MODE0 |                                                                                                                            | 0 |  |  |  |  |

| MODE             | 1   | PS_MODE1 | The boot mode can be selected according to table 11-1 of the Technical Reference Manual of the Zyng UltraScale+ Device [1] | 1 |  |  |  |  |

| (SW800)          | 2   | PS_MODE2 |                                                                                                                            | 0 |  |  |  |  |

|                  | 3   | PS_MODE3 |                                                                                                                            | 0 |  |  |  |  |

Table 5: MODE switch

The PS\_MODE switches (0-3) can be set to ON (logical value = 0) or OFF (logical value = 1). The values of all switches in the package are interpreted as one number, as read from switch 3 to 0. The following table shows the positions of the switches that must be configured for the different boot modes.

| Boot Mode      | Mode Pins<br>[3:0] | Switch Position of Mode Pin Description |     |     | on  |                     |                       |

|----------------|--------------------|-----------------------------------------|-----|-----|-----|---------------------|-----------------------|

|                | [3.0]              | 3                                       | 2   | 1   | 0   | ·                   |                       |

| Quad-SPI (24b) | 0001               | ON                                      | ON  | ON  | OFF | 24-bit addressing   |                       |

| Quad-SPI (32b) | 0010               | ON                                      | ON  | OFF | ON  | 32-bit addressing   | (Default on delivery) |

| SD0 (2.0)      | 0101               | ON                                      | OFF | ON  | OFF | SD 2.0              |                       |

| eMMC (1.8V)    | 0110               | ON                                      | OFF | OFF | ON  | eMMC version 4.5 at | t 1.8V                |

Table 6: MODE switch configuration

Please note, that the numbering of the mode pins is indicated on the PCB as shown in Figure 6! Ignore the numbers on the DIP switch housing.

### 4.1.2 PROG, SRST, POR

The XMC-CPU/Zulu comes with the 3 reset buttons (SMD tactile switches): PROG, SRST and POR, see Figure 6, page 17. For further information about the reset signals see Technical Reference Manual of the Zynq UltraScale+ Device [1].

| Reset<br>Button     | Pin       | Direction | Description                             |

|---------------------|-----------|-----------|-----------------------------------------|

| <b>PROG</b> (SW820) | PS_PROG_B | I/O       | PL configuration reset signal           |

| <b>SRST</b> (SW812) | PS_SRST_B | Input     | System reset commonly used during debug |

| <b>POR</b> (SW813)  | PS_POR_B  | Input     | Power-on reset signal                   |

Table 7: Reset signals

### 5 Hardware Installation

#### NOTICE

Read the safety instructions at the beginning of this document carefully before you start with the hardware installation!

#### WARNING

Hazardous Voltage - Risk of electric shock due to unintentional contact with uninsulated live parts with high voltages inside of the system into which the XMC-CPU/Zulu is to be integrated.

- → Disconnect all hazardous voltages (mains voltage) before opening the system. Never carry out work while power supply voltage is switched on!

- → Ensure the absence of voltage before starting any electrical work.

#### NOTICE

Electrostatic discharges may cause damage to electronic components.

- → To avoid this, please discharge the static electricity from your body *before* you touch the XMC-CPU/Zulu.

- → Furthermore, you should prevent your clothes from touching the XMC-CPU/Zulu, because your clothes might be electrostatically charged as well.

#### **Procedure:**

- 1. Switch off your system and all connected peripheral devices (monitor, printer, etc.).

- 2. Discharge your body as described above.

- Disconnect the system from the mains.

Make sure that no risk arises from the system into which the XMC-CPU/Zulu shall be inserted.

#### WARNING

Hazardous Voltage

**Risk of electric shock** due to unintentional contact with uninsulated live parts with high voltages.

- → Disconnect all hazardous voltages (mains voltage) before opening the system.

- → If the system does not have a flexible mains cable, but is directly connected to mains, disconnect the power supply via the safety fuse and make sure that the fuse cannot switch on again unintentionally (e.g. with caution label).

- → Ensure the absence of voltage before starting any electrical work.

- → Cover or block off adjacent live parts.

- 4. Open the case if necessary.

- 5. For sufficient EMC shielding the XMC-CPU/Zulu shall make contact to the system's enclosure nearly completely around its front panel. For this purpose, a conductive O-ring is contained in the product package of the XMC-CPU/Zulu module. Mount the conductive O-ring on the front panel of the XMC-CPU/Zulu. Additionally, or instead of it use shielding material as for example conductive shielding gasket.

- 6. Make sure that the XMC-CPU/Zulu is configured according to your needs:

- For the configuration of the hardware see chapter "Coding Switch and Reset Buttons" on page 17.

#### **Hardware Installation**

7. Remove your carrier board (if already installed) and plug the XMC-CPU/Zulu carefully on the carrier board. Pay attention that the XMC-CPU/Zulu is correctly installed on the carrier board.

#### NOTICE

Please note that the number of mating cycles of the XMC connectors P5 and P6 is only 10! Do not uninstall the XMC-CPU/Zulu from the carrier board if it is not absolutely necessary!

Fix the XMC-CPU/Zulu with the screws on the carrier board. Use the four M 2.5 x 5 mm screws which are contained in the product package of the module.

- 8. Install the carrier board in your system.

- 9. Connect the Ethernet and the CON interface via the connectors in the front panel of the XMC-CPU/Zulu.

- 10. Close the system's case again (if applicable).

- 11. Connect the system to mains again (mains connector or safety fuse).

- 12. Switch on the system and the peripheral devices.

- 13. End of hardware installation.

- 14. Set the interface properties in your operating system. Refer to the documentation of the operating system.

# **6 Technical Data**

### 6.1 General Technical Data

|                             | Nominal voltag                                                                                   | ge: 3                                                                               | 3.3 V                  | $I_{3.3V\_MAX} = 640 \text{ mA},$                                | I <sub>3.3V_TYPICAL</sub> = 610 mA                                     |  |

|-----------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------|------------------------------------------------------------------------|--|

| Power supply voltage        |                                                                                                  | 5<br>C<br>1                                                                         | /PWF<br>5V<br>or<br>2V | $I_{5V\_MAX} = 830 \text{ mA},$ $I_{12V\_MAX} = 400 \text{ mA},$ | $I_{5V\_TYPICAL} = 720 \text{ mA}$ $I_{12V\_TYPICAL} = 340 \text{ mA}$ |  |

|                             |                                                                                                  | -                                                                                   |                        | $P_{3.3V+5V\_MAX} = 10 \text{ W}$                                |                                                                        |  |

| Power consumption           | Typical: < 10 \<br>Maximum: 10                                                                   |                                                                                     |                        | ntest)                                                           |                                                                        |  |

| Temperature range           | Operation: 0 ° Storage: -40 ° Transport: -40                                                     | C + 85                                                                              | °C                     | mbient temperature                                               |                                                                        |  |

| Humidity                    | Max. 90%, noi                                                                                    | n-conden                                                                            | sing                   |                                                                  |                                                                        |  |

|                             | ETH0<br>ETH1                                                                                     |                                                                                     |                        |                                                                  | : 1000) - Ethernet Port 0<br>: 1000) - Ethernet Port 1                 |  |

|                             | CON Mini USB socket type-B (X1220, MUSB-05-S-B-SM-A, Mating cycles: 1500) - Console (USB-Device) |                                                                                     |                        |                                                                  |                                                                        |  |

|                             | PMC P4<br>XMC P5<br>XMC P6                                                                       | P5 XMC connector (Samtec ASP-103614-04, mating cycles: 10) - PCI Express interface, |                        |                                                                  |                                                                        |  |

| Connector                   | Only for test- and programming purposes:                                                         |                                                                                     |                        |                                                                  |                                                                        |  |

|                             | CPU Debug                                                                                        |                                                                                     |                        | l107-02-F-D-BE (passace CPU                                      | -thru micro socket, X800),                                             |  |

|                             | Connectors for factory use only:                                                                 |                                                                                     |                        |                                                                  |                                                                        |  |

|                             | SYS Mon.                                                                                         | Samtec: CLM104-02-F-D-BE (pass-thru micro socket, X810), - SYSMON                   |                        |                                                                  |                                                                        |  |

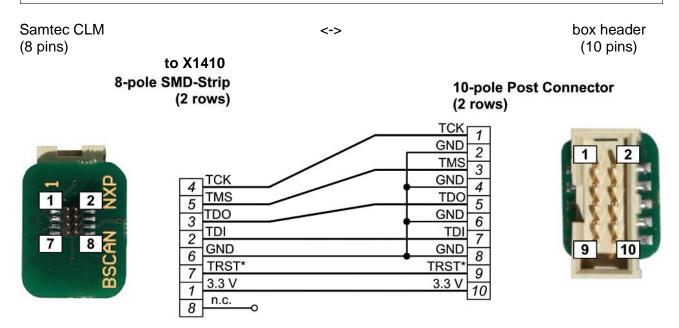

|                             | JTAG ETH                                                                                         | Samtec: CLM104-02-F-D-BE (pass-thru micro socket, X1410), - JTAG interface Ethernet |                        |                                                                  |                                                                        |  |

|                             | Voltage<br>Meas.                                                                                 |                                                                                     |                        |                                                                  |                                                                        |  |

| Form factor /<br>Dimensions | 149 mm x 74 mm x 10 mm (without front panel)                                                     |                                                                                     |                        |                                                                  |                                                                        |  |

| Weight                      | Ca. 120 g (without heat sink)                                                                    |                                                                                     |                        |                                                                  |                                                                        |  |

Table 8: General Data of the module

### 6.2 CPU Kernel

| Architecture        | Dual Core A53 Application Processor Unit (APU) + Dual Core Real-time Processor Unit.                                                                      |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                 | XILINX Zynq UltraScale+ CG<br>XCZU2CG-1SFVA625E – 2x APU, 2x RPU                                                                                          |

| Clock rate          | 1.3 GHz APU,<br>533 MHz RPU                                                                                                                               |

| Programmable Logics | Internal FPGA resources: 103K System Logic Cells, 94K CLB Flip Flops, 47K CLB LUTs                                                                        |

| RAM                 | Organisation: 2 devices each 16 bit, no ECC<br>Series: 2Gbyte – 2x MT40A512M16                                                                            |

| Flash memory (NOR)  | Organisation: 2 devices with Quad SPI Interface (Dual Quad SPI) 64Mbyte – 2x MT25QU256ABA1EW7-0SIT 100 000 read / write cycles, > 20 years data retention |

| Flash memory (NAND) | 16 Gbyte eMMC memory<br>e.g.: Swissbit (SFEM4096B1EA1TO-I-GE-111-E02)                                                                                     |

| EEPROM              | 1 x 128 Kbit for U-Boot Environment  Via I <sup>2</sup> C in Fast (400kHz) Mode 1 000 000 read / write cycles, >20 years data retention                   |

Table 9: CPU Kernel

### 6.3 Ethernet Interface PS

| Number of Ethernet interfaces | 2                                                                                                                                                                                                                      |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standard                      | IEEE 802.3, 10BASE-T, 100BASE-TX, 1000BASE-T                                                                                                                                                                           |

| Bit rate                      | 10/100/1000 Mbit/s                                                                                                                                                                                                     |

| Controller                    | Integrated in the PS (Processing System) section of the CPU                                                                                                                                                            |

| Connection                    | Twisted Pair (compatible with IEEE 802.3), 1000BASE-T,                                                                                                                                                                 |

| Electrical isolation          | 1x via transformer integrated in the RJ45 socket Electrical strength 1500V AC / 60sec 1 x without electrical isolation                                                                                                 |

| Connector                     | 1x RJ45 socket in the front panel with integrated LEDs (Link- and Activity) and integrated transformer 1x via P6                                                                                                       |

| Topology                      | The interface PS-GEM3 of the controller integrated in the CPU is connected to the front panel as ETH1, interface PS-GEM2 is connected to connector P6. A common MDIO interface is used for all interfaces (PS and PL). |

| PTP                           | It is possible to synchronise the device time by means of the IEEE1588 conformant PTP protocol via this Ethernet interface.                                                                                            |

Table 10: Data of the Ethernet interface PS

### 6.4 Ethernet Interface PL

| Number of Ethernet interfaces | 2                                                                                                                                                                                                                                                                       |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standard                      | IEEE 802.3, 10BASE-T, 100BASE-TX, 1000BASE-T                                                                                                                                                                                                                            |

| Bit rate                      | 10/100/1000 Mbit/s                                                                                                                                                                                                                                                      |

| Controller                    | Integrated in the PS section and routed via the PL (Programmable Logic) section of the CPU or embedded as IP core in the PL section of the CPU                                                                                                                          |

| Connection                    | Twisted Pair (compatible with IEEE 802.3), 1000BASE-T,                                                                                                                                                                                                                  |

| Electrical isolation          | 1x via transformer integrated in the RJ45 socket Electrical strength 1500V AC / 60sec 1 x without electrical isolation                                                                                                                                                  |

| Connector                     | 1x RJ45 socket in the front panel with integrated LEDs (Link- and Activity) and integrated transformer 1x via P6                                                                                                                                                        |

| Topology                      | The CPU integrated controllers are used instead of using the IP core as controller, thus the interface PS-GEM0 is connected to the front panel as ETH0, interface PS-GEM1 is connected to connector P6. A common MDIO interface is used for all interfaces (PS and PL). |

| PTP                           | It is possible to synchronise the device time by means of the IEEE1588 conformant PTP protocol via this Ethernet interface.                                                                                                                                             |

Table 11: Data of the Ethernet interface PL

# 6.5 USB Console Port (CON)

| Number             | 1 asynchronous serial interface, used as terminal interface            |                                                                      |  |

|--------------------|------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| Controller         | Integrated in CPU                                                      |                                                                      |  |

| Bit rate           | Value range:<br>Default setting:                                       | 9600 Baud 115200 Baud<br>115200 Baud, 8 Bit, No Parity<br>1 Stop-Bit |  |

| Physical Interface | UART serial console transformed to USB 1.1 via USB to serial converter |                                                                      |  |

| Software           | Standard operating-system driver                                       |                                                                      |  |

| Connector          | MiniUSB Type-B                                                         |                                                                      |  |

Table 12: Data of the USB console port

### 6.6 PCle Interfaces

| Number           | 1                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Controller       | Integrated in the PS section of the CPU                                                                                                                                                 |

| Standard         | VITA 42.0  Notice: The CPU can support PCle 2.0. If the usage of PCle 2.0 via the VITA 42 connectors should cause problems, it is possible to limit the usage to PCle 1.1 via software. |

| Lanes            | 4                                                                                                                                                                                       |

| Mode             | Endpoint or Root Complex (defined by the base board via XMC pin DP19+ on XMC_J15)                                                                                                       |

| Software support | As Root Complex: Standard operating system drivers As Endpoint: Access to a shared memory section                                                                                       |

| Connector        | P5                                                                                                                                                                                      |

Table 13: Data of the PCle interface

# 6.7 Digital Inputs/Outputs P4

| Number                    | Maximum 62, see chapter "PMC P4 I/O Connector" page 31 for assignment                                                                                                                                      |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO Configuration          | Single ended or differential inputs or outputs, depending on FPGA pin configuration.  Routed as differential pair in the layout                                                                            |

| Physical interface        | 1.8V to 3.3V level shifters or FET switches for LVDS signals can be alternatively enabled via FPGA by groups of 8 pins. Connections are visible on page 31.  On request only: 0 Ohm resistors as fallback, |

| Input switching threshold | 3,3V LVTTL, not 5V tolerant or 1,8V LVDS according to XILINX data sheet                                                                                                                                    |

| Bandwidth                 | 3,3V LVTTL: max. 60 Mbps<br>1,8 LVDS: max. 500MHz bandwidth                                                                                                                                                |

| Electrical isolation      | None                                                                                                                                                                                                       |

| Protective circuit        | None                                                                                                                                                                                                       |

| Connector                 | P4                                                                                                                                                                                                         |

Table 14: Data of the Digital I/Os on P4

### 6.8 Digital Inputs/Outputs P6

| Number                    | Maximum 62, see chapter "XMC – P6 I/O Connector" page 34 for assignment                    |  |

|---------------------------|--------------------------------------------------------------------------------------------|--|

| IO Configuration          | Single ended or differential inputs or outputs, depending on FPGA pin configuration.       |  |

|                           | Routed as differential pair in the layout                                                  |  |

| Physical interface        | FPGA directly connected to P6                                                              |  |

| Input switching threshold | 1.8V LVTTL, not tolerant for 2.5V / 3.3V or 5V or 1.8V LVDS according to XILINX data sheet |  |

| Bandwidth                 | According to XILINX data sheet                                                             |  |

| Electrical isolation      | None                                                                                       |  |

| Protective circuit        | None                                                                                       |  |

| Connector                 | P6                                                                                         |  |

Table 15: Data of the Digital I/Os on P6

### **6.9 Control Elements**

| Buttons | 3 SMD tactile switches for the signals SRST, PROG and POR (Power On Reset) are equipped on the bottom layer of the XMC-CPU/Zulu (see Figure 6 page 17).                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Switch  | 4-bit DIP-switch MODE for the configuration of the boot modes. (Together with the SD-card slot for initial system start-up). The DIP switch is equipped on the bottom layer of the XMC-CPU/Zulu see Figure 6 page 17). |

Table 16: Data of the control elements and display elements

### 6.10 Health

| Voltage              | Internal voltages of the PS and PL sections via the CPU internal SYSMON Unit (see XILINX data sheet)                                                                                                                                                                                                                                                                                                                                          |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature          | 3 CPU internal sensors of the SYSMON unit (see XILINX data sheet) + 3 external I <sup>2</sup> C temperature sensors, one with alert output ports. The 3 external I <sup>2</sup> C sensors are connected to the I <sup>2</sup> C bus 2: One TMP100 each at I <sup>2</sup> C address 0x4a and 0x4b One ADT7461 at address 0x4c. This has one internal temperature sensor and a connection to the CPU diode for CPU-DIE temperature measurement. |

| XMC-IPMI support     | Not supported                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Digital IO extension | For sideband signals of the PMC/XMC bus as e.g.: Root, Monarch, Wake, Reset, Connected via an I <sup>2</sup> C IO expander respectively direct to the FPGA Pins                                                                                                                                                                                                                                                                               |

| Power<br>Management  | Voltage regulator and clock distribution component are connected to the CPU via I <sup>2</sup> C. It is possible to request or set various characteristic values                                                                                                                                                                                                                                                                              |

| Board Type           | Board revision and variant can be requested via FPGA IO pins and external resistors                                                                                                                                                                                                                                                                                                                                                           |

Table 17: Health unit

### 6.11 Mass Storage

| Number     | 1                                       |

|------------|-----------------------------------------|

| Standard   | eMMC specification 4.51                 |

| Topology   | Directly connected to the CPU           |

| Controller | Integrated in the PS section of the CPU |

| Capacity   | 16 Gbyte maximum capacity               |

| Data rate  | HS200 mode (theoretically 1660 Mbyte/s) |

Table 18: Data of the mass storage unit

### 6.12 MicroSD Card Slot

| Number          | 1                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------|

| Standard        | Compatible with the SD Host Controller Specification revision 3.0 (SDHC)                                           |

| Topology        | Directly connected to the CPU                                                                                      |

| Controller      | Integrated into the PS section of the CPU                                                                          |

| Data rate       | SDR104 mode (theoretically 800Mbyte/s)                                                                             |

| Supported media | The usability of individual media (manufacturer, type, size) depends on the technology used and cannot be granted. |

| Functionality   | This slot is intended for the initial start-up only (Bare Metal bring up)                                          |

Table 19: Data of the MicroSD card slot

### 6.13 Front Panel LEDs

| Device                   | Texas TLC59116                                                                                                                                                                   |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connection               | Via I <sup>2</sup> C to PL: I <sup>2</sup> C SCL on pin G6,<br>I <sup>2</sup> C SDA on Pin H6,<br>Reset on Pin D8                                                                |

| I <sup>2</sup> C address | 0x60                                                                                                                                                                             |

| LED colour               | Each tricolour LED has its separate three inputs from the TCL59116. The first connection is wired to the green LED, the second one to the red LED and the third to the blue LED. |

Table 20: Front panel LEDs

### 6.14 PCI Clock Generator

| Device                   | IDT 5P49V5935B                                                                                                                                                                                                      |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connection               | Control via I <sup>2</sup> C 1 Clock output 13 can be used for PCIe Clock input to CPU PS if operating in ROOT Complex mode. Output 4 is connected to PL (E6 CLK_P, E5 CLK_N) and can be used for user application. |

| I <sup>2</sup> C address | 0x6A                                                                                                                                                                                                                |

| Configuration            | Please contact our support team ( <a href="mailto:support@esd.eu">support@esd.eu</a> ) if you want to use the external clock feature.                                                                               |

Table 21: PCI Clock generator

# **6.15 Optional Interfaces**

### 6.15.1 CAN Interfaces

| Number of CAN interfaces | 2                                                                                                               |

|--------------------------|-----------------------------------------------------------------------------------------------------------------|

| Topology                 | Parallel connection of RX and TX signals to the PS pins and to the PL pins.                                     |

| CAN controller           | Acc. to ISO 11898-1<br>Configurable per software from PS or as esdACC IP-core integrated in the<br>FPGA section |

| CAN protocol             | According to ISO 11898-1                                                                                        |

| Physical Layer           | External                                                                                                        |

| Electrical isolation     | None / If required the CAN interfaces have to be electrically isolated externally                               |

| Bus termination          | A terminating resistor has to be set externally, if required                                                    |

| Connector                | Via P4                                                                                                          |

Table 22: Data of the optional CAN interfaces

### 6.15.2 PMC Interface

| Number           | 1                                                                                              |

|------------------|------------------------------------------------------------------------------------------------|

| Controller       | Pericom PI7C9X111SLBFDE PCIe to PCI Bridge                                                     |

| Standard         | IEEE1386 (PCI 3.0)                                                                             |

| Version          | 32 Bit, 33/66MHz, 3.3V, 5V tolerant                                                            |

| Mode             | Monarch or Non-Monarch (defined by the base board via pin)                                     |

| Software support | As Monarch: Standard operating system driver As Non-Monarch: Access to a Shared Memory section |

| Connector        | P1 and P2                                                                                      |

Table 23: Data of the optional PMC interface

# **7 Connector Assignments**

### 7.1 PMC/XMC Connectors

### 7.1.1 PMC P1 Connector

| Pin | Signal         | Signal          | Pin |

|-----|----------------|-----------------|-----|

| 1   | TCK            | -12V            | 2   |

| 3   | GND            | INTA#           | 4   |

| 5   | INTB#          | INTC#           | 6   |

| 7   | GND (PRESENT#) | +5V             | 8   |

| 9   | INTD#          | n.c. (reserved) | 10  |

| 11  | GND            | n.c. (reserved) | 12  |

| 13  | PCI-CLK        | GND             | 14  |

| 15  | GND            | GNT#            | 16  |

| 17  | REQ#           | +5V             | 18  |

| 19  | VIO            | AD[31]          | 20  |

| 21  | AD[28]         | AD[27]          | 22  |

| 23  | AD[25]         | GND             | 24  |

| 25  | GND            | C/BE3#          | 26  |

| 27  | AD[22]         | AD[21]          | 28  |

| 29  | AD[19]         | +5V             | 30  |

| 31  | VIO            | AD[17]          | 32  |

| 33  | FRAME#         | GND             | 34  |

| 35  | GND            | IRDY#           | 36  |

| 37  | DEVSEL#        | +5V             | 38  |

| 39  | GND            | n.c. (LOCK#)    | 40  |

| 41  | n.c. (SDONE#)  | n.c. (SBO)      | 42  |

| 43  | PAR            | GND             | 44  |

| 45  | VIO            | AD[15]          | 46  |

| 47  | AD[12]         | AD[11]          | 48  |

| 49  | AD[09]         | +5V             | 50  |

| 51  | GND            | C/BE0#          | 52  |

| 53  | AD[06]         | AD[05]          | 54  |

| 55  | AD[04]         | GND             | 56  |

| 57  | VIO            | AD[03]          | 58  |

| 59  | AD[02]         | AD[01]          | 60  |

| 61  | AD[00]         | +5V             | 62  |

| 63  | GND            | n.c. (REQ64#)   | 64  |

### 7.1.2 PMC P2 Connector

| Pin | Signal          | Signal          | Pin |

|-----|-----------------|-----------------|-----|

| 1   | +12V            | TRST#           | 2   |

| 3   | TMS             | TDO             | 4   |

| 5   | TDI             | GND             | 6   |

| 7   | GND             | n.c. (reserved) | 8   |

| 9   | n.c. (reserved) | n.c. (reserved) | 10  |

| 11  | MODE2#          | +3.3V           | 12  |

| 13  | PCI-RST#        | MODE3#          | 14  |

| 15  | +3.3V           | MODE4#          | 16  |

| 17  | n.c. (PME#)     | GND             | 18  |

| 19  | AD[30]          | AD[29]          | 20  |

| 21  | GND             | AD[26]          | 22  |

| 23  | AD[24]          | +3.3V           | 24  |

| 25  | IDSEL           | AD[23]          | 26  |

| 27  | +3.3V           | AD[20]          | 28  |

| 29  | AD[18]          | GND             | 30  |

| 31  | AD[16]          | C/BE2#          | 32  |

| 33  | GND             | IDSELB          | 34  |

| 35  | TRDY#           | +3.3V           | 36  |

| 37  | GND             | STOP#           | 38  |

| 39  | PERR#           | GND             | 40  |

| 41  | +3.3V           | SERR#           | 42  |

| 43  | C/BE1#          | GND             | 44  |

| 45  | AD[14]          | AD[13]          | 46  |

| 47  | M66EN           | AD[10]          | 48  |

| 49  | AD[08]          | +3.3V           | 50  |

| 51  | AD[07]          | n.c. (REQB#)    | 52  |

| 53  | +3.3V           | GNTB#           | 54  |

| 55  | n.c. (reserved) | GND             | 56  |

| 57  | n.c. (reserved) | EREADY          | 58  |

| 59  | GND             | RESETOUT#       | 60  |

| 61  | n.c. (ACK64#)   | +3.3V           | 62  |

| 63  | GND             | MONARCH#        | 64  |

### 7.1.3 PMC P4 I/O Connector

| Pin | Signal<br>Name | Notes    | Alternative<br>Signal Name | Differential Pair (XILINX Name) | Notes     |

|-----|----------------|----------|----------------------------|---------------------------------|-----------|

| 1   | FPGA-IO<0>     | IO, T/L0 |                            | IO_L20N_T3L_N3_AD1N_66          |           |

| 2   | FPGA-IO<1>     | IO, T/L0 |                            | IO_L23N_T3U_N9_66               |           |

| 3   | FPGA-IO<2>     | IO, T/L0 |                            | IO_L20P_T3L_N2_AD1P_66          |           |

| 4   | FPGA-IO<3>     | IO, T/L0 |                            | IO_L23P_T3U_N8_66               |           |

| 5   | FPGA-IO<4>     | IO, T/L0 |                            | IO_L21N_T3L_N5_AD8N_66          |           |

| 6   | FPGA-IO<5>     | IO, T/L0 |                            | IO_L24N_T3U_N11_PERSTN0_65      |           |

| 7   | FPGA-IO<6>     | IO, T/L0 |                            | IO_L21P_T3L_N4_AD8P_66          |           |

| 8   | FPGA-IO<7>     | IO, T/L1 |                            | IO_L24P_T3U_N10_PERSTN1_I2C_S   |           |

| 9   | FPGA-IO<8>     | IO, T/L1 |                            | IO_L21N_T3L_N5_AD8N_65          |           |

| 10  | FPGA-IO<9>     | IO, T/L1 |                            | IO_L19N_T3L_N1_DBC_AD9N_65      |           |

| 11  | FPGA-IO<10>    | IO, T/L1 |                            | IO_L21P_T3L_N4_AD8P_65          |           |

| 12  | FPGA-IO<11>    | IO, T/L1 |                            | IO_L19P_T3L_N0_DBC_AD9P_65      |           |

| 13  | FPGA-IO<12>    | IO, T/L1 |                            | IO_L12N_T1U_N11_GC_65           | CLK Input |

| 14  | FPGA-IO<13>    | IO, T/L1 |                            | IO_L22N_T3U_N7_DBC_AD0N_65      |           |

| 15  | FPGA-IO<14>    | IO, T/L1 |                            | IO_L12P_T1U_N10_GC_65           | CLK Input |

| 16  | FPGA-IO<15>    | IO, T/L1 |                            | IO_L22P_T3U_N6_DBC_AD0P_65      |           |

| 17  | FPGA-IO<16>    | IO, T/L2 |                            | IO_L22N_T3U_N7_DBC_AD0N_66      |           |

| 18  | FPGA-IO<17>    | IO, T/L2 |                            | IO_L15N_T2L_N5_AD11N_66         |           |

| 19  | FPGA-IO<18>    | IO, T/L2 |                            | IO_L22P_T3U_N6_DBC_AD0P_66      |           |

| 20  | FPGA-IO<19>    | IO, T/L2 |                            | IO_L15P_T2L_N4_AD11P_66         |           |

| 21  | FPGA-IO<20>    | IO, T/L2 |                            | IO_L24N_T3U_N11_66              |           |

| 22  | FPGA-IO<21>    | IO, T/L2 |                            | IO_L10N_T1U_N7_QBC_AD4N_65      |           |

| 23  | FPGA-IO<22>    | IO, T/L2 |                            | IO_L24P_T3U_N10_66              |           |

| 24  | FPGA-IO<23>    | IO, T/L2 |                            | IO_L10P_T1U_N6_QBC_AD4P_65      |           |

| 25  | FPGA-IO<24>    | IO, T/L3 |                            | IO_L19N_T3L_N1_DBC_AD9N_66      |           |

| 26  | FPGA-IO<25>    | IO, T/L3 |                            | IO_L14N_T2L_N3_GC_65            | CLK Input |

| 27  | FPGA-IO<26>    | IO, T/L3 |                            | IO_L19P_T3L_N0_DBC_AD9P_66      |           |

| 28  | FPGA-IO<27>    | IO, T/L3 |                            | IO_L14P_T2L_N2_GC_65            | CLK Input |