# **TQMC700** Reconfigurable FPGA with AD/DA & Digital I/O

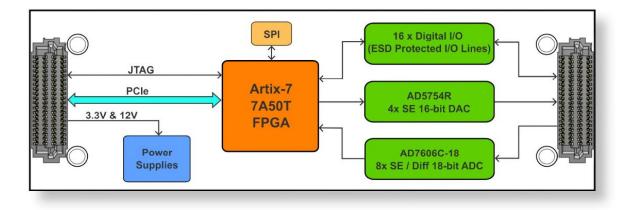

TQMC700 Block Diagram

# **Application Information**

The TQMC700 is a VITA93.0 compatible single-width QMC offering a user programmable AMD Artix 7 7A50T FPGA.

The TQMC700 provides 16 ESD-protected 5V-tolerant TTL lines. All I/O lines are individually programmable as input or output. TTL I/O lines can be set to high, low, or tristate. Each TTL I/O line has a pull-resistor to a common programmable pull-up voltage that can be set to +3.3 V, +5 V and GND.

The 18 bit ADC offers 8 input channels, each of them has a sampling rate of up to 1 Msps. Each channel can be operated in bipolar single-ended, unipolar single-ended and bipolar differential mode. In the single-ended modes it offers software selectable input voltage ranges of 0-5 V, 0-10 V, 0-12.5 V,  $\pm 2.5$  V,  $\pm 5$  V,  $\pm 6.25$  V,  $\pm 10$  V and  $\pm 12.5$ V. In differential mode the input voltages are selectable between  $\pm 5$  V,  $\pm 10$  V,  $\pm 12.5$  V and  $\pm 20$  V. There is a flexible digital filter offering a oversampling ratio up to 256.

The DAC offers 4 channels of 16 bit analog outputs with software selectable output voltage ranges of 0-5 V, 0-10 V, 0-10.8 V,  $\pm$ 5 V,  $\pm$ 10 V or  $\pm$ 10.8 V. The output voltage range can be individually set per channel. The conversion

time is typ. 10  $\mu s$  and the DAC outputs are capable to drive a load of 2 k $\Omega,$  with a capacitance up to 4000 pF.

Each TQMC700 is factory calibrated. The calibration information is stored in an on-board serial EEPROM unique to each TQMC700 module.

The User FPGA is configured by a SPI flash. An in-circuit debugging option is available via the QMC's JTAG interface for read back and real-time debugging of the FPGA design (using the Vivado ILA).

User applications for the TQMC700 with 7A50T FPGA can be developed using the design software Vivado Design Suite HL WebPACK Edition, which can be downloaded free of charge from <u>www.xilinx.com</u>.

TEWS offers a well-documented basic FPGA Example Application design. It includes a constraints file with all necessary pin assignments and basic timing constraints. The example design covers the main functionalities of the TQMC700. It implements PCIe to register mapping and basic I/O. It comes as a Xilinx Vivado Design Suite project with source code and as a ready-to-download bit stream.

Ehlbeek 15a 30938 Burgwedel fon 05139-9980-0 fax 05139-9980-49

www.powerbridge.de info@powerbridge.de

TEWS Technologies GmbH keeps the right to change technical specification without further notice. All trademarks mentioned are property of their respective owners.

Tel. 05139-9980-0

Fax 05139-9980-49

Issue 1.0.0 07.05.2025

**DIN EN ISO**

9001:2015 14001:2015

certified V

powerBridge Computer Vertriebs GmbH

Geschäftsführer Fabio Görke

WEEE-Reg.-Nr. DE 23 438 792

Bankverbindung: Hannoversche Volksbank BIC: VOHADE2HXXX

IBAN DE69 2519 0001 0014 4789 00 (EUR) IBAN DE42 2519 0001 0014 4789 01 (USD)

# **Technical Information**

- Form Factor: Standard single QMC conforming to VITA 93.0

- O Board size: 78.25 mm x 26 mm

- O PCI Express 2.0 compliant interface

- O Artix-7 User programmable FPGA

- O Xilinx XC7A50T-2

- PCIe endpoint in FPGA

- O 128 Mbit SPI-EEPROM for FPGA configuration and

- O User Data

- O Digital I/O

0

- O 16 ESD-protected 5 V-tolerant TTL lines with programmable pull- resistor

- O Direction individually programmable

- 8 channels 18 bit analog input

- O Simultaneous sampling

- O differential or single-ended inputs

- O Programmable input voltage (one setting for all channels):

- 0-5 V, 0-10 V, 0-12.5 V,

- ±2.5 V, ±5 V, ±6.25 V, ±10 V, ±12.5 V

- O Sampling rate: 1 Msps

- O Overvoltage protection

- O Factory calibration

- O 4 channels single-ended 16 bit analog output

- O Simultaneous update

- O Programmable output voltage: 0-5 V, 0-10 V, 0-10.8 V, ±5 V, ±10 V, ±10.8 V

- O Conversion time: typ.10 µs

- O Up to 2 k $\Omega$  resistive, 4000 pF capacitive load

- O Overcurrent protection

- O Factory calibration

- O Operating temperature -40 °C to +85 °C

# **Order Information**

#### **RoHS Compliant**

**TPMC700-10R-A**16 TTL I/O, 8 AD, 4 DA, Artix-7 7A50T FPGA, air cooled**TPMC700-10R-H**16 TTL I/O, 8 AD, 4 DA, Artix-7 7A50T FPGA, conduction cooled

For the availability of non-RoHS compliant (leaded solder) products please contact TEWS.

#### Software

| TDRV020-SW-25 | Integrity Software Support |

|---------------|----------------------------|

| TDRV020-SW-42 | VxWorks Software Support   |

| TDRV020-SW-65 | Windows Software Support   |

| TDRV020-SW-82 | Linux Software Support     |

| TDRV020-SW-95 | QNX Software Support       |

For other operating systems please contact TEWS.

### **Related Products**

TPCE210

2 Site QMC Carrier, PCIe x4, Gen2, low-profile, VHDCI-68 I/O

TEWS Technologies GmbH keeps the right to change technical specification without further notice. All trademarks mentioned are property of their respective owners. Issue 1.0.0 07.05.2025

# TEWS Technologies GmbH Eggerstedter Weg 14, 25421 Pinneberg, Germany Phone: At 49 (0) 4 101 4058 0 Bank 30938 Burgwed ho@tewsteenNr.16(WWW.tews.com Bank USI.1d.-Nr. DE 811 558 186 BIC: BIC:

100% paperless company powerBridge Computer Vertriebs GmbH

Geschäftsführer Fabio Görke

Tel. 05139-9980-0 Fax 05139-9980-49 WEEE-Re

WEEE-Reg.-Nr. DE 23 438 792

Bankverbindung: Hannoversche Volksbank BIC: VOHADE2HXXX

IBAN DE69 2519 0001 0014 4789 00 (EUR) IBAN DE42 2519 0001 0014 4789 01 (USD)