TECHNISCHE BESCHREIBUNG

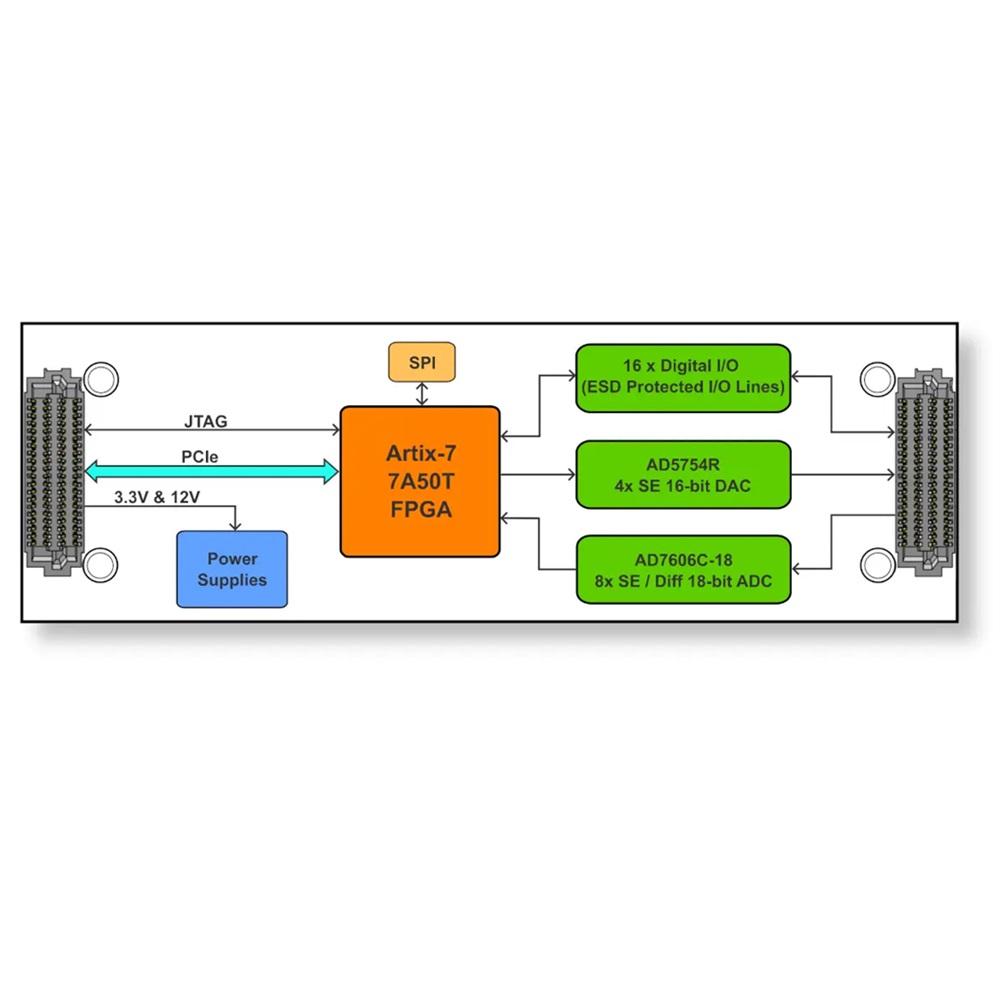

- QMC-Modul, VITA 93.0 konform, PCIe 2.0 konform

- Xilinx Artix 7 FPGA (XC7A50T-2)

- Digital I/O-Leitungen: 16 ESD-geschützte 5V-tolerante TTL-I/Os mit progr. Pull-Up Widerstand, individuell als Ein-/Ausgang programmierbar

- 8 18-bit ADC-Analogeingänge:

- Simultanes Sampling

- Differential- oder Single-Ended-Eingänge

- Programmierbare Eingangsspannung (eine Einstellung für alle Kanäle): 0-5V, 0-10V, 0-12.5V, ±2.5V, ±5V, ±6.25V, ±10V, ±12.5V

- 1 MSPS Samplingrate

- Überspannungsschutz

- Werkskalibrierung

- 4 Single-Ended 16-bit DAC-Analogausgänge

- Simultane Updates

- Programmierbare Ausgangsspannung: 0-5V, 0-10V, 0-10.8V, ±5V, ±10V, ±10.8V

- Konversionszeit: typ. 10µs

- Bis zu 2kΩ resistiv, 4000pF kapazitive Belastung

- Überstromschutz

- Werkskalibrierung

- 128 Mbit SPI-EEPROM für FPGA Konfiguration und Anwenderdaten

- -40°C .. +85°C Betriebstemperaturbereich

- Integrity, Windows, Linux, QNX und VxWorks Treiber lieferbar

- 5 Jahre Garantie

Bestellbezeichnungen

TPMC700-10R-A

Arix-7 FPGA QMC-Modul

TPMC700-10R-H

Arix-7 FPGA QMC-Modul, conduction-cooled

TDRV020-SW-25

Integrity Treiber

TDRV020-SW-42

VxWorks Treiber

TDRV020-SW-65

Windows Treiber

TDRV020-SW-82

Linux Treiber

TDRV020-SW-95

QNX Treiber