Technical Description

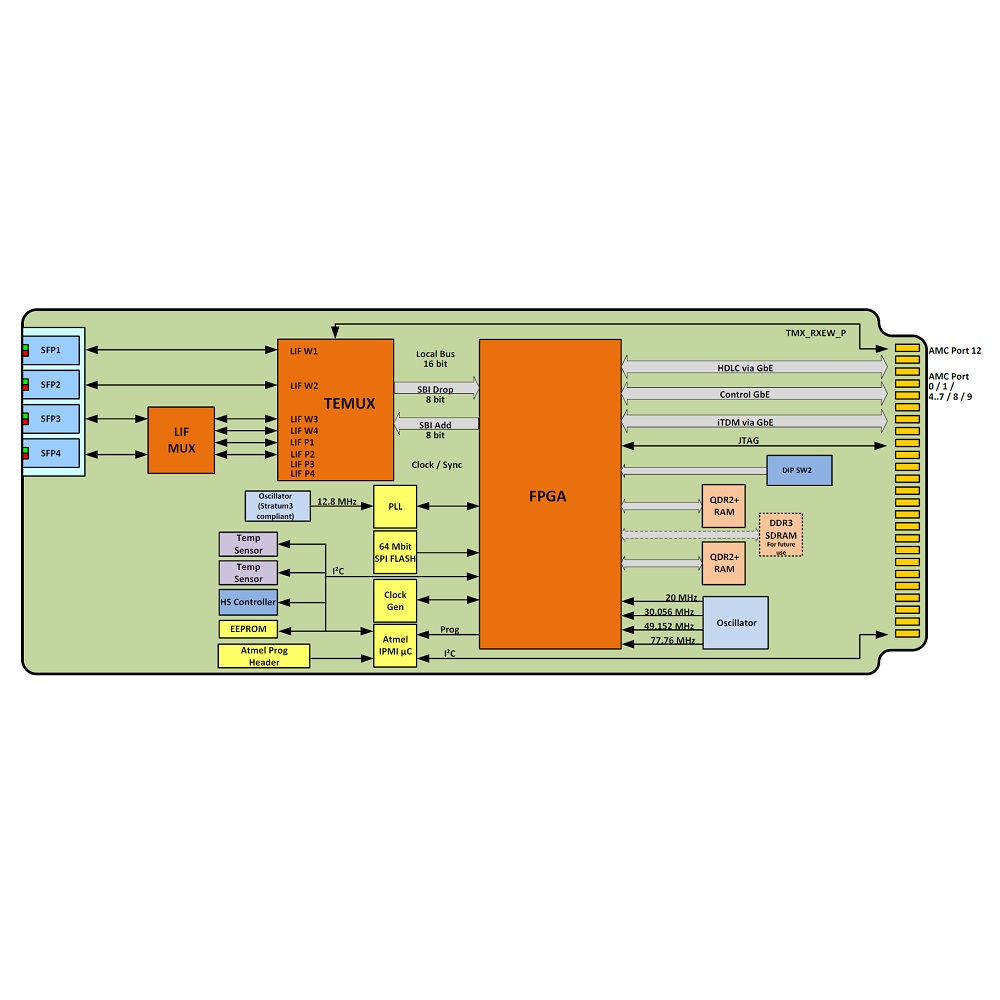

- AMC Line Interface between SDH/SONET and TDM

- AMC module with AMC.2 type 2 E2 interface, mid size or full size form factor

- XILINX Kintex 7 XC7K325T or KC7K160T

- SDH interface

- Time slot interchanger (TSI)

- iTDM controller

- Control interface

- Ethernet interfaces

- Opt. HDLC controller

- 2GB DDR3 SDRAM for FPGA

- Opt. two 72Mbit QDR2+ SRAMs for FPGA

- TEMUX336 add/drop multiplexer/demultiplexer

- Four OC-3/STM-1 or two OC-12/STM-4 framers

- 252 E1 or 336 T1 streams incl. respective clocking information contained in a single STM-1 or STM-4 SDH frame

- VT1.5/VT-2 or TU-11/TU-12 to VC3/VC4/VC4-4c or STM4/STM4c supported mappings

- VSF, SLC-96 and ESF T1 framing standards

- G.704 and G.706 (CRC-4 multiframe) E1 framing standards

- Four optical 155 Mbit/s OC-3/STM-1 or two 622 Mbit/s OC-12/STM-4 line interfaces in the front panel

- 4 Gigabit Ethernet interfaces AMC at ports 0, 1, 4 and 8

- Opt. fat pipe (XAUI or SRIO) at AMC ports 4-7

- 1000BaseBX iTDM interface

- Configuration/control via Ethernet

- Typ. power consumption 3.3V, 12V, 20W

- 0°C .. +50°C operating temperature range

- 2 years warranty

Order Information

NAMC-SDH-00SN

AMC line interface, KC7K325T FPGA

NAMC-SDH-01SN

AMC line interface, KC7K325T FPGA, 72Mbit QDR2+ SRAM

NAMC-SDH-02SN

AMC line interface, KC7K325T FPGA, 2x 72Mbit QDR2+ SRAMs

NAMC-SDH-10SN

AMC line interface, KC7K160T FPGA

NAMC-SDH-11SN

AMC line interface, KC7K160T FPGA, 72Mbit QDR2+ SRAM

NAMC-SDH-12SN

AMC line interface, KC7K160T FPGA, 2x 72Mbit QDR2+ SRAMs

S=0

No transceiver

S=1

STM1 (OC-3)

S=2

STM4 (OC-12)

N=0

No transceiver

N=1

1 STM1 or STM4 transceiver

N=2

2 STM1 or STM4 transceiver

N=3

3 STM1 transceiver

N=4

4 STM1 transceiver